# THE FOUNDATIONS FOR A SCALEABLE METHODOLOGY FOR SYSTEMS DESIGN

by

Toby Myers

B.Eng(hons), B.InfTech

# School of Information and Communication Technology Science, Environment, Engineering and Technology Griffith University

Submitted in fulfillment of the requirements of the degree of

DOCTOR OF PHILOSOPHY

March 2010

#### Abstract

Marketplace demand is driving the need to develop software systems of ever increasing scale. Managing the complexity created by this increasing scale is crucial. Failure to adequately address the complexity that emerges with increasing scale can play havoc with even the most simple of tasks. Mainstream software & systems engineering approaches are struggling to manage the complexity of building large-scale software-intensive systems which is resulting in the widespread failure of projects. These failures are the result of two deficiencies in mainstream approaches. Firstly, these approaches utilise abstraction to manage complexity. Abstraction is a temporary solution which just delays the re-emergence of complexity until the approach is applied to larger systems. Secondly, these approaches do not provide a clear path from the requirements of a system to a final work product. It is common instead for a miraculous leap of intuition to occur from the initial requirements to a specification, a design or a deployed system. To ensure requirements are met, the resulting work product then must be iteratively re-evaluated against the requirements and corrected until it achieves acceptable quality. This construct-by-correction approach results in unnecessary rework, and can be overwhelmed by the complexity of large-scale systems.

The objective of this dissertation is to address the issue of scaleability in software & systems engineering by providing the foundations for a scaleable, widely applicable, end-to-end methodology. To achieve this we have extended Behavior Engineering (BE), which is an integrated approach to systems development that supports the engineering of large-scale dependable sofware intensive systems at both the systems and software engineering level. BE uses a bottom-up process that enables each requirement to be modeled independently

iv

and integrated one at a time to form a complete view of the system specification that is built out of the requirements. Current research involving BE focuses primarily on using BE models as a formal specification, which can then be further analysed using techniques such as model-checking. This dissertation extends BE by providing a new design stage developed within a model driven engineering framework.

The resulting end-to-end methodology is demonstrated using three case studies intended to show a wide cross-cutting of applications. In the first case study, the extended BE approach is demonstrated by deploying a BE design on an embedded controller.

In the second case study, the BE approach is combined with Modelica, a mathematical modeling language. Together, BE and Modelica are used to develop a new approach called Co-Modeling, which involves the development of systems composed of integrated software and hardware components. Co-modeling is demonstrated with a case study involving the development of an automated train protection system which monitors a train driver and takes control of the train if a dangerous situation is not responded to. The developed co-model is used to investigate co-modeling scenarios and to determine the effect that various combinations of sensors, actuators and hardware platforms have on the behavior of the integrated system.

The third case study introduces a migration approach to dealing with legacy systems which uses a BE model as an intermediary. The approach is demonstrated using a real-world case study from industry. The outdated circuitry is captured in a BE model using a domain-specific extension and used to generate VHDL, a hardware description language. To demonstrate the benefit of using BE as an intermediary, the BE model is also used to perform failure mode and effects analysis, a procedure more commonly applied to BE models developed from software requirements.

Together these case studies demonstrate the potential of using a scaleable methodology to manage the complexity of designing the software-intensive systems of software & systems engineering.

#### Declaration

This work has not previously been submitted for a degree or diploma in any university. To the best of my knowledge and belief, the thesis contains no material previously published or written by another person except where due reference is made in the thesis itself.

Toby Myers

vi Declaration

#### Acknowledgements

I would like to gratefully acknowledge the support I have received from many people during the preparation and writing of this disseration. First and foremost, I would like to convey my sincere gratitude to my supervisor, Professor Geoff Dromey, for his unwaivering support and encouragement throughout this project. Your recent passing away has saddened many people and I feel honoured for the time you gave to teach me, even in your failing health. This work could not have come to fruition without the opportunities you provided. I would also like to thank my associate supervisor, Professor Vladmir Estiville-Castro, for taking over supervision duties towards the end of this dissertation.

I extend my thanks to my colleages working on the Building Dependability into Complex Computer-Based Systems project including Nisansala Yatapanage, Kirsten Winter, Robert Colvin, Lars Grunske, Ian J. Hayes, Peter Lindsay, Lian Wen, Diana Kirk, John Seagrott and Saad Zafar. The contributions each you have made created a strong foundation on which to base this work. I also thank you all for the robust discussions at our weekly meetings, and for your advice which helped shape this dissertation. In addition I would like to thank Joern Guy Suss for introducing me to the Eclipse Integrated Development Environment.

I would like to thank my family for their patience and understanding during the substantial time it took to complete this project. I particularly want to thank my wife, Toni and my son, David for providing me with such a loving and supportive environment whilst I undertook this work.

Finally, I would like to acknowledge the financial assistance provided by Griffith University and Raytheon Australia during the course of this project.

#### List of Publications

- Myers, T., Fritzson, P., Dromey, R.G. Co-Modeling: From Requirements to an Integrated Software/Hardware Model. (submitted to IEEE Computer Magazine)

- Myers, T., Dromey, R. G. (2009), From Requirements to Embedded Software Formalising the Key Steps, in Proceedings of the 2009 Australian Software Engineering Conference (ASWEC'09), Gold Coast, Australia, 14-17 April, pp. 23-33.

- Myers, T., Fritzson, P., Dromey, R. G. (2008), Seamlessly Integrating Software & Hardware Modelling for Large-Scale Systems, in Proceedings of the 2nd International Workshop on Equation-Based Object-Oriented Languages and Tools, Paphos, Cyprus, July 8, pp. 5-15.

- Myers, T. J., Noel, T., Parent, M., Vlacic, L. (2005), Autonomous Motion of a Driverless Vehicle operating among Dynamic Obstacles, in Proceedings of the 44th IEEE Conference on Decision and Control, and the European Control Conference 2005 (CDC-ECC'05), 12-15 December, Seville, Spain, pp. 5071- 5076.

- Myers, T. J., Vlacic, L., Noel, T., Parent, M. (2005), Autonomous driving in a timevarying environment, in the 2005 IEEE Workshop on Advanced Robotics and its Social Impacts, Nagoya, Japan, 12-15 June, pp. 53-58.

<sup>&</sup>lt;sup>1</sup>These publications are unrelated to the topic of this dissertation but were completed during candidature.

### Dedication

I dedicate this work to my father, may you rest forever peaceful, frolicking through the elysian fields.

xii Dedication

#### Contents

| $\mathbf{A}$    | bstra       | ct                      |  |  |  |     | iii          |

|-----------------|-------------|-------------------------|--|--|--|-----|--------------|

| D               | eclar       | ation                   |  |  |  |     | $\mathbf{v}$ |

| $\mathbf{A}$    | cknov       | wledgements             |  |  |  |     | vii          |

| Li              | ${f st}$ of | Publications            |  |  |  |     | ix           |

| D               | edica       | tion                    |  |  |  |     | xi           |

| List of Figures |             |                         |  |  |  | xix |              |

| List of Tables  |             |                         |  |  |  | XXV |              |

| Sı              | ıpple       | mentary Material        |  |  |  | X   | xvii         |

| Ι               | Int         | troduction & Background |  |  |  |     | 1            |

| 1               | Intr        | oduction                |  |  |  |     | 3            |

|                 | 1.1         | Objective and Approach  |  |  |  |     | 7            |

|                 | 1.2         | Thesis Hypotheses       |  |  |  |     | 11           |

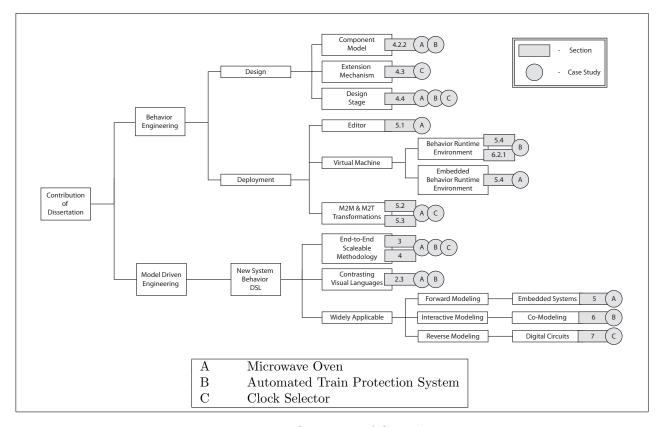

|                 | 1.3         | Contribution            |  |  |  |     | 13           |

|                 | 1.4         | Thesis Structure        |  |  |  |     | 14           |

XiV CONTENTS

| 2 | $\mathbf{A}\mathbf{n}$ | Overview of Model Driven Engineering             | 17 |

|---|------------------------|--------------------------------------------------|----|

|   | 2.1                    | Origins and Goals of MDE                         | 18 |

|   | 2.2                    | Model Driven Engineering Approaches              | 21 |

|   |                        | 2.2.1 Meta-Modeling and the Meta-Object Facility | 23 |

|   |                        | 2.2.2 The UML Platform-Independent Model         | 26 |

|   |                        | 2.2.3 Executable UML                             | 30 |

|   | 2.3                    | A New MDE GPL for System Behavior                | 32 |

|   |                        | 2.3.1 Representing System Behavior               | 33 |

|   |                        | 2.3.2 Using a Scaleable Methodology              | 46 |

|   |                        | 2.3.3 Extension Mechanism                        | 51 |

|   | 2.4                    | Conclusion                                       | 54 |

| 3 | Intr                   | roduction to Behavior Engineering                | 57 |

|   | 3.1                    | Overview of the Behavior Modeling Language       | 59 |

|   |                        | 3.1.1 Behavior Trees                             | 59 |

|   |                        | 3.1.2 Composition Trees                          | 66 |

|   | 3.2                    | Overview of the Behavior Modeling Process        | 67 |

|   |                        | 3.2.1 Formalisation                              | 68 |

|   |                        | 3.2.2 Testing Fitness for Purpose                | 71 |

|   |                        | 3.2.3 Specification                              | 73 |

|   | 3.3                    | Modeling the Simple Microwave Oven               | 75 |

|   |                        | 3.3.1 Formalisation                              | 76 |

|   |                        | 3.3.2 Testing Fitness for Purpose                | 81 |

|   |                        | 3.3.3 Specification                              | 84 |

|   | 3.4                    | Related Research                                 | 90 |

|   | 3.5                    | Discussion                                       | 91 |

|   | 3.6                    | Conclusion                                       | 91 |

| 4 | Des                    | sign with Behavior Engineering                   | 93 |

|   | 4.1                    | Why Design With Behavior Engineering             | 94 |

|   | 4.2                    | Deploying a BE Model                             | 97 |

Contents

|    |                                                           | 4.2.1 Replicating Hardware Success with Software Components                                                                                                                                                                                                                                     | <br>97                                                          |

|----|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|    |                                                           | 4.2.2 The BE Component Model                                                                                                                                                                                                                                                                    | <br>100                                                         |

|    | 4.3                                                       | An Extension Mechanism for BE                                                                                                                                                                                                                                                                   | <br>103                                                         |

|    | 4.4                                                       | The Design Stage of the BMP                                                                                                                                                                                                                                                                     | <br>105                                                         |

|    |                                                           | 4.4.1 Resolving the System/Environment Boundary                                                                                                                                                                                                                                                 | <br>105                                                         |

|    |                                                           | 4.4.2 Resolving the System/Component Boundary                                                                                                                                                                                                                                                   | <br>107                                                         |

|    |                                                           | 4.4.3 The Deployment Composition Tree                                                                                                                                                                                                                                                           | <br>108                                                         |

|    | 4.5                                                       | Designing the Simple Microwave Oven                                                                                                                                                                                                                                                             | <br>108                                                         |

|    | 4.6                                                       | A Previous Approach to Design with BE                                                                                                                                                                                                                                                           | <br>112                                                         |

|    | 4.7                                                       | Discussion                                                                                                                                                                                                                                                                                      | <br>115                                                         |

|    | 4.8                                                       | Conclusion                                                                                                                                                                                                                                                                                      | <br>116                                                         |

|    |                                                           |                                                                                                                                                                                                                                                                                                 |                                                                 |

| ΙΙ | F                                                         | Forward Modeling                                                                                                                                                                                                                                                                                | 119                                                             |

| 5  | Beh                                                       | navior Engineering of Embedded Systems                                                                                                                                                                                                                                                          | 121                                                             |

|    |                                                           |                                                                                                                                                                                                                                                                                                 |                                                                 |

|    | 5.1                                                       | The BE EMF Editor                                                                                                                                                                                                                                                                               |                                                                 |

|    | 5.1<br>5.2                                                | The BE EMF Editor                                                                                                                                                                                                                                                                               | 125                                                             |

|    |                                                           |                                                                                                                                                                                                                                                                                                 | <br>125<br>128                                                  |

|    |                                                           | Model-to-Model Transformations                                                                                                                                                                                                                                                                  | <br>125<br>128<br>130                                           |

|    |                                                           | Model-to-Model Transformations                                                                                                                                                                                                                                                                  | <br>125<br>128<br>130<br>134                                    |

|    | 5.2                                                       | Model-to-Model Transformations                                                                                                                                                                                                                                                                  | <br>125<br>128<br>130<br>134                                    |

|    | 5.2                                                       | Model-to-Model Transformations          5.2.1 The BT M2M Transformation Language          5.2.2 Implementing M2M Transformations in ATL          Model-to-Text Transformations                                                                                                                  | <br>125<br>128<br>130<br>134<br>137                             |

|    | 5.2                                                       | Model-to-Model Transformations          5.2.1 The BT M2M Transformation Language          5.2.2 Implementing M2M Transformations in ATL          Model-to-Text Transformations          5.3.1 M2T transformation of the Behavior Tree                                                           | <br>125<br>128<br>130<br>134<br>137<br>137                      |

|    | 5.2                                                       | Model-to-Model Transformations          5.2.1 The BT M2M Transformation Language          5.2.2 Implementing M2M Transformations in ATL          Model-to-Text Transformations          5.3.1 M2T transformation of the Behavior Tree          5.3.2 M2T transformation of the Composition Tree | <br>125<br>128<br>130<br>134<br>137<br>137<br>138<br>140        |

|    | <ul><li>5.2</li><li>5.3</li><li>5.4</li></ul>             | Model-to-Model Transformations                                                                                                                                                                                                                                                                  | <br>125<br>128<br>130<br>134<br>137<br>137<br>138<br>140<br>144 |

|    | <ul><li>5.2</li><li>5.3</li><li>5.4</li><li>5.5</li></ul> | Model-to-Model Transformations                                                                                                                                                                                                                                                                  | <br>125<br>128<br>130<br>134<br>137<br>138<br>140<br>144<br>147 |

| 11 | 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                    | Model-to-Model Transformations                                                                                                                                                                                                                                                                  | <br>125<br>128<br>130<br>134<br>137<br>138<br>140<br>144<br>147 |

xvi Contents

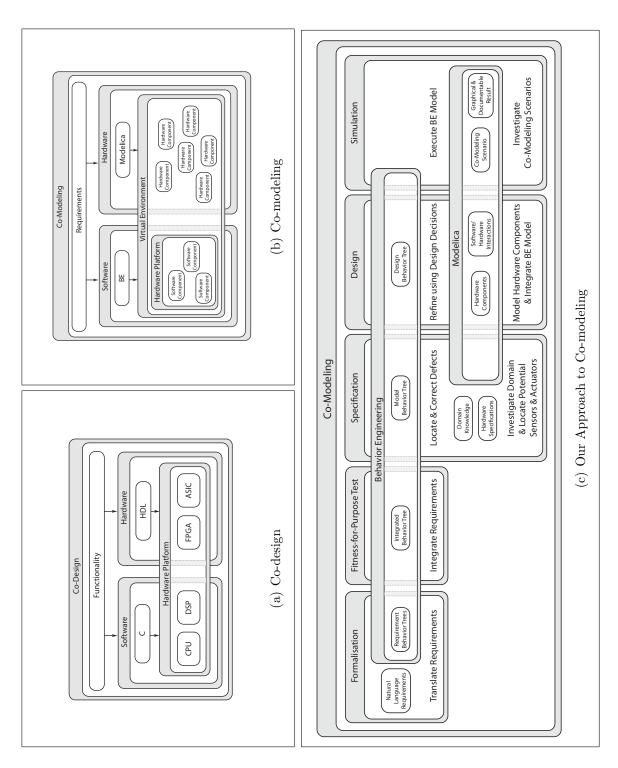

|    | 6.1 | From    | Co-design to Co-modeling                                 | 155         |

|----|-----|---------|----------------------------------------------------------|-------------|

|    | 6.2 | Consti  | ructing a Co-Model                                       | 159         |

|    |     | 6.2.1   | Modeling the Requirements                                | 159         |

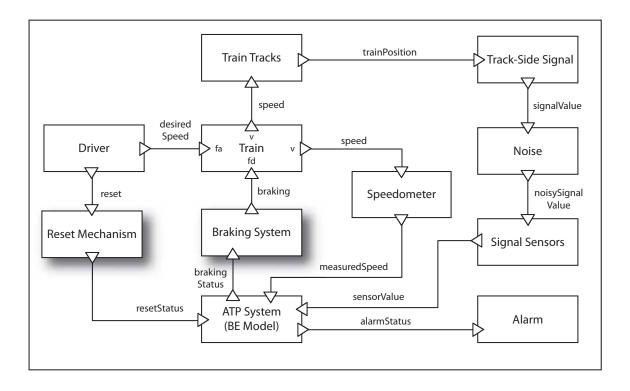

|    |     | 6.2.2   | Building a Virtual Environment                           | 175         |

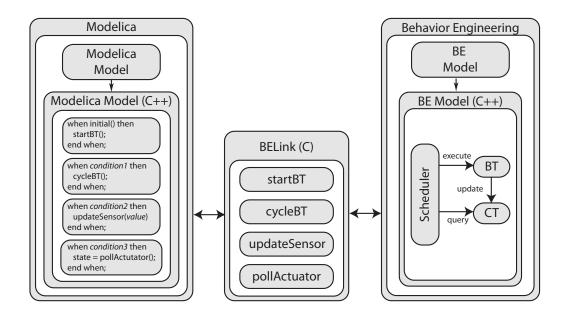

|    |     | 6.2.3   | Implementing Software/Hardware Interactions              | 179         |

|    | 6.3 | Explo   | ring the Possibilities                                   | 181         |

|    | 6.4 | Towar   | ds Co-modeling of Cyber-Physical Systems                 | 185         |

|    | 6.5 | Discus  | ssion                                                    | 186         |

|    | 6.6 | Conclu  | usion                                                    | 186         |

| IJ | V I | Rever   | se Modeling 1                                            | 89          |

| 7  | Beh | avior 1 | Engineering of Digital Circuits 1                        | L <b>91</b> |

|    | 7.1 | Captu   | ring Digital Circuits with BTs                           | 194         |

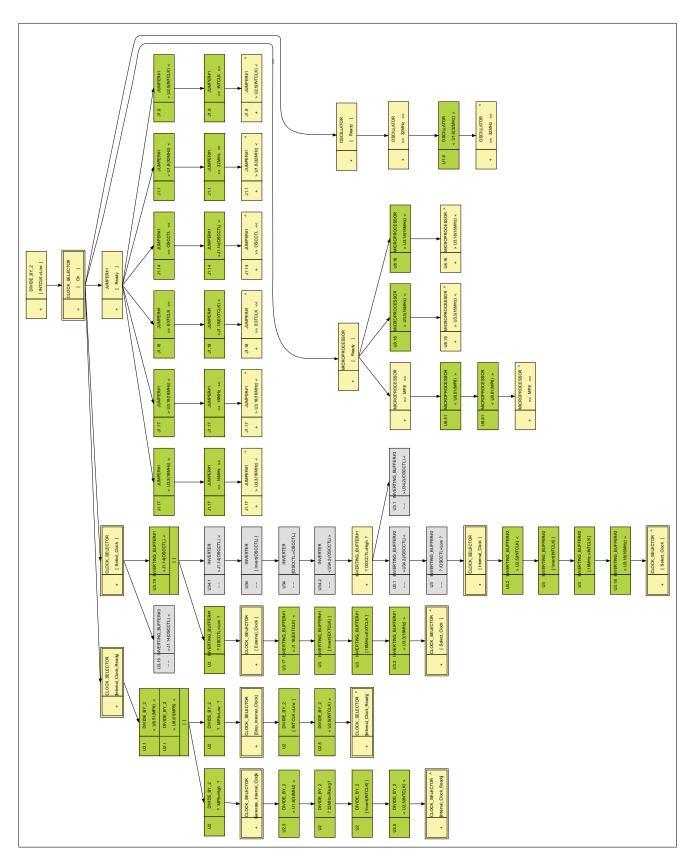

|    | 7.2 | Replic  | eating Legacy Hardware with BE                           | 200         |

|    |     | 7.2.1   | Translating a Hardware Requirement                       | 202         |

|    |     | 7.2.2   | Testing Fitness for Purpose                              | 207         |

|    |     | 7.2.3   | Specification                                            | 210         |

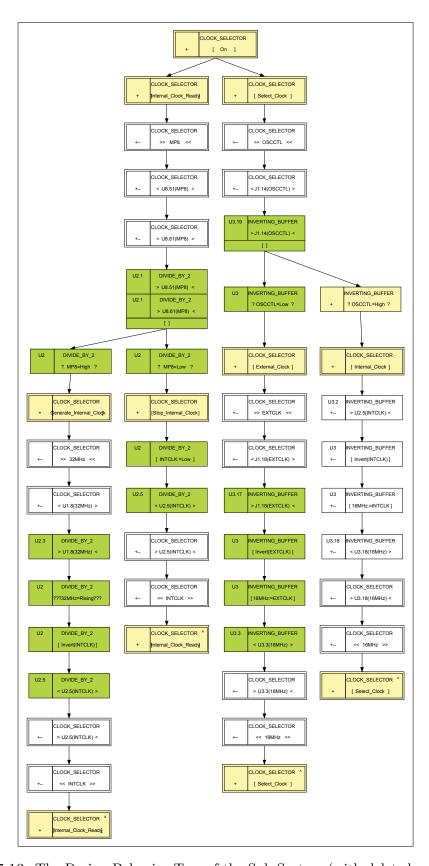

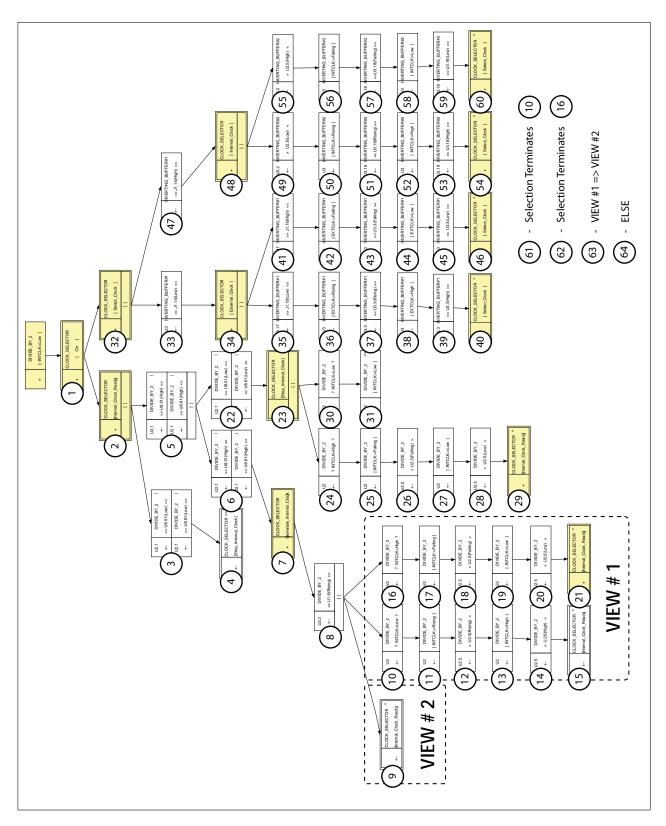

|    |     | 7.2.4   | Design                                                   | 212         |

|    | 7.3 | Perfor  | ming Failure Modes and Effects Analysis                  | 215         |

|    |     | 7.3.1   | Modifying the MBT for Performing Model-Checking          | 215         |

|    |     | 7.3.2   | Results of Performing Failure Modes and Effects Analysis | 218         |

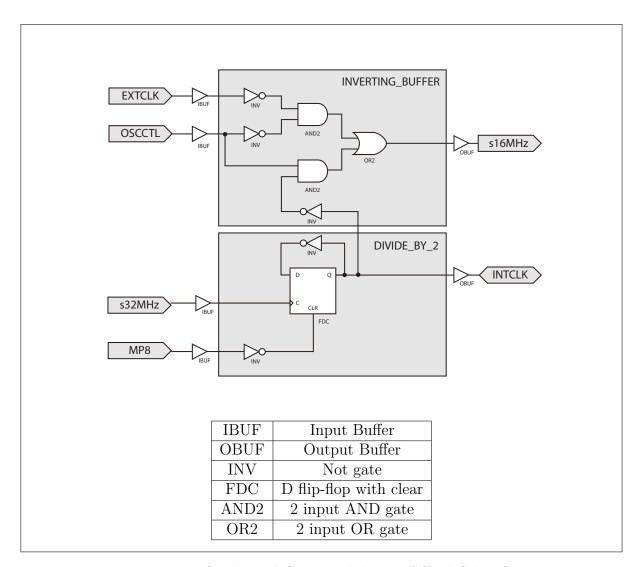

|    | 7.4 | Simula  | ation and Synthesis                                      | 219         |

|    |     | 7.4.1   | Generating VHDL Code                                     | 220         |

|    |     | 7.4.2   | Simulation                                               | 224         |

|    |     | 7.4.3   | Synthesis                                                | 225         |

|    | 7.5 | Discus  | ssion                                                    | 227         |

|    | 7.6 | Conclu  | usion                                                    | 228         |

Contents

| $\mathbf{V}$ | D              | iscus         | sion                                 |      |   | 231 |

|--------------|----------------|---------------|--------------------------------------|------|---|-----|

| 8            | Disc           | cussion       | 1                                    |      |   | 233 |

|              | 8.1            | A Scal        | leable Methodology for System Design | <br> |   | 234 |

|              | 8.2            | Compa         | arison with Related Work             |      |   | 235 |

|              | 8.3            | Contri        | ibution                              | <br> |   | 237 |

|              | 8.4            | Future        | e Work                               | <br> |   | 239 |

| $\mathbf{V}$ | $\mathbf{I}$ A | <b>A</b> pper | ndices                               |      |   | 243 |

| $\mathbf{A}$ | Con            | ıtrastir      | ng BTs with other visual languages   |      |   | 245 |

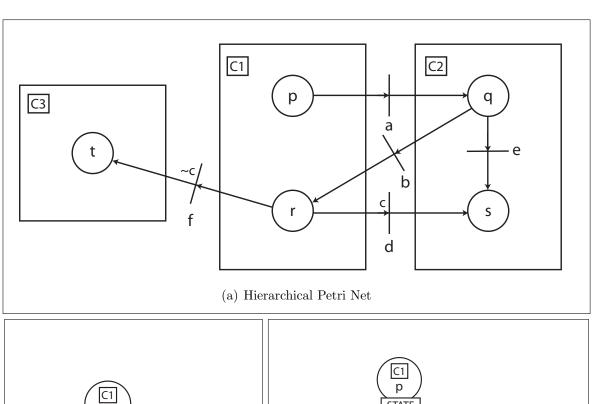

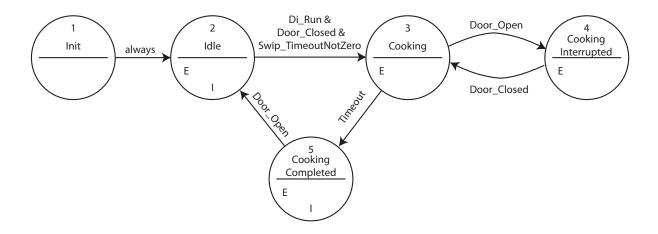

|              | A.1            | Case S        | Study I: State Machines              | <br> |   | 246 |

|              |                | A.1.1         | Transitions                          | <br> |   | 248 |

|              |                | A.1.2         | Segmentation                         | <br> |   | 249 |

|              |                | A.1.3         | Methodology                          | <br> |   | 249 |

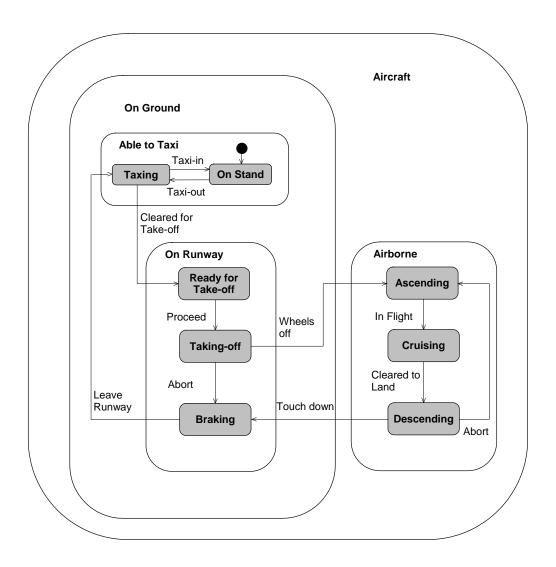

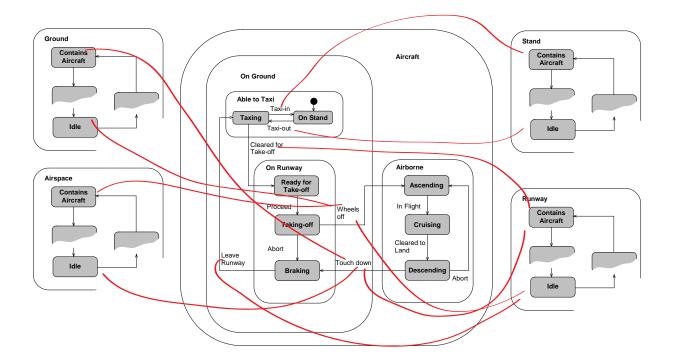

|              | A.2            | Case S        | Study II: StateCharts                | <br> |   | 250 |

|              |                | A.2.1         | Transitions                          | <br> |   | 252 |

|              |                | A.2.2         | Segmentation                         | <br> |   | 253 |

|              |                | A.2.3         | Methodology                          | <br> |   | 253 |

|              | A.3            | Case S        | Study III: Exogenous Connectors      | <br> |   | 260 |

|              |                | A.3.1         | Transitions                          | <br> |   | 261 |

|              |                | A.3.2         | Segmentation                         | <br> |   | 263 |

|              |                | A.3.3         | Methodology                          | <br> | • | 263 |

| В            | Beh            | avior '       | Tree Language                        |      |   | 267 |

|              | B.1            | Namin         | ng Conventions                       | <br> |   | 268 |

|              |                | B.1.1         | Variable Naming Conventions          | <br> |   | 268 |

|              |                | B.1.2         | Node Naming Conventions              | <br> |   | 269 |

|              |                | B.1.3         | Relation Naming Conventions          | <br> |   | 270 |

|              |                | B.1.4         | Tree Naming Conventions              | <br> |   | 271 |

|              |                | B.1.5         | Tree Branch Naming Convention        | <br> |   | 272 |

xviii Contents

|              | B.2         | Behav   | ior Tree Notation & Syntax          |   | 273         |  |

|--------------|-------------|---------|-------------------------------------|---|-------------|--|

|              |             | B.2.1   | Node Tags                           |   | 273         |  |

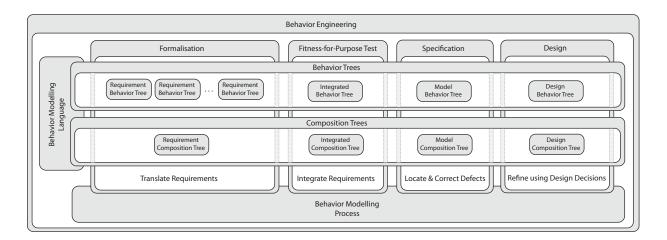

|              |             | B.2.2   | Basic Nodes                         |   | 274         |  |

|              |             | B.2.3   | Behavior Tree Composition           |   | 275         |  |

|              |             | B.2.4   | Node Operators                      |   | 276         |  |

| $\mathbf{C}$ | Inve        | estigat | ing the Hardware Component Model    |   | 277         |  |

| D            | Beh         | avior ' | Tree Model-to-Model Transformations |   | 285         |  |

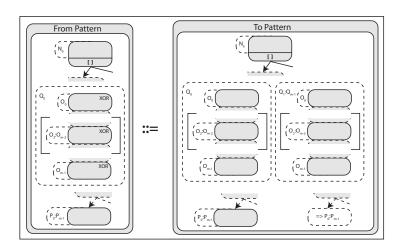

|              | D.1         | Conju   | nction Transformation Rule          |   | 286         |  |

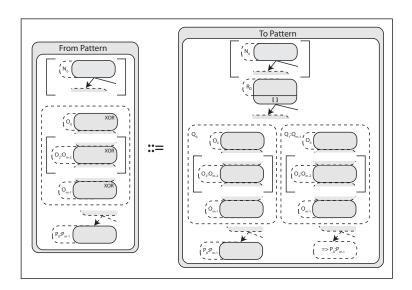

|              | D.2         | Disjun  | ction Transformation Rule           |   | 287         |  |

|              | D.3         | Exclus  | sive OR Transformation Rule         |   | 288         |  |

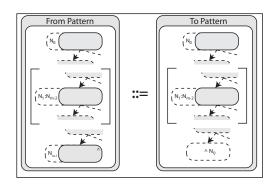

|              | D.4         | Revers  | sion Transformation Rule            |   | 289         |  |

|              | D.5         | Refere  | nce Transformation Rule             |   | 289         |  |

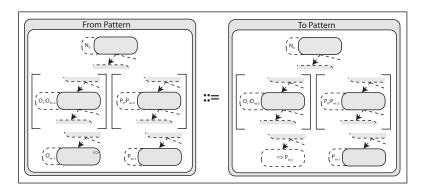

|              | D.6         | Brancl  | h-Kill Transformation Rule          |   | 290         |  |

|              | D.7         | Synch   | ronisation Transformation Rule      | • | 290         |  |

| Re           | efere       | nces    |                                     |   | <b>2</b> 91 |  |

| $\mathbf{G}$ | Glossary 30 |         |                                     |   |             |  |

| A            | crony       | ms      |                                     |   | 315         |  |

| In           | dex         | dex 32  |                                     |   |             |  |

## List of Figures

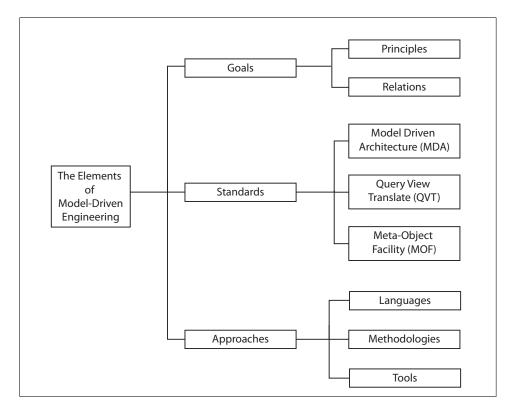

| 2.1  | An Overview of the elements of MDE                             | 20 |

|------|----------------------------------------------------------------|----|

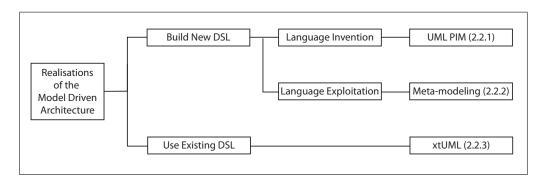

| 2.2  | MDA Approaches                                                 | 23 |

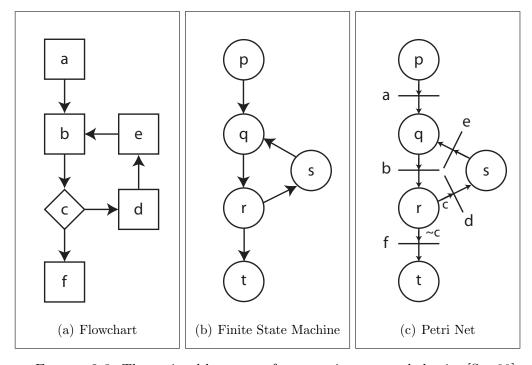

| 2.3  | Three visual languages for capturing system behavior [Sow00]   | 34 |

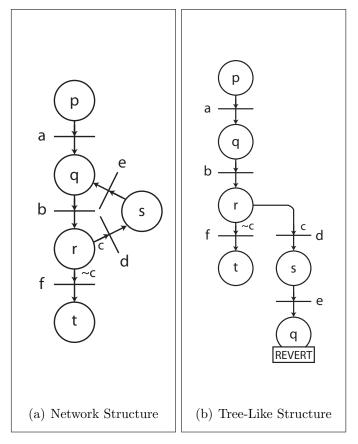

| 2.4  | Network Structure versus Tree-Like Structure                   | 36 |

| 2.5  | Segmentation and Transitions in a Petri Net                    | 38 |

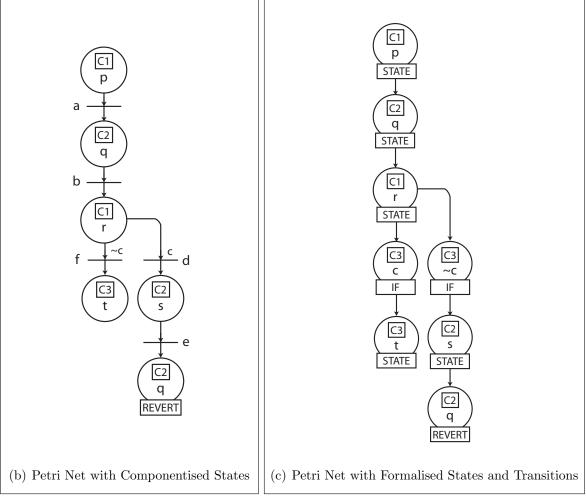

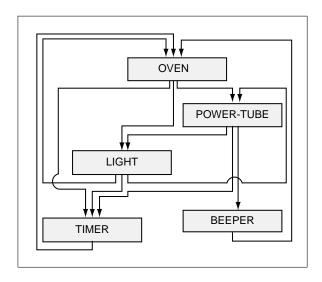

| 3.1  | An Outline of Behavior Engineering                             | 59 |

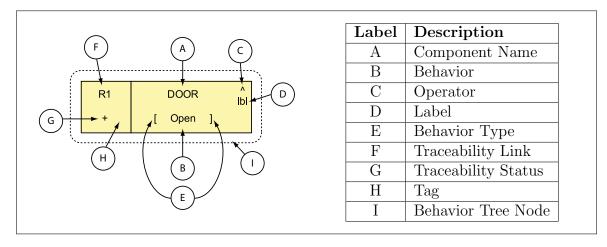

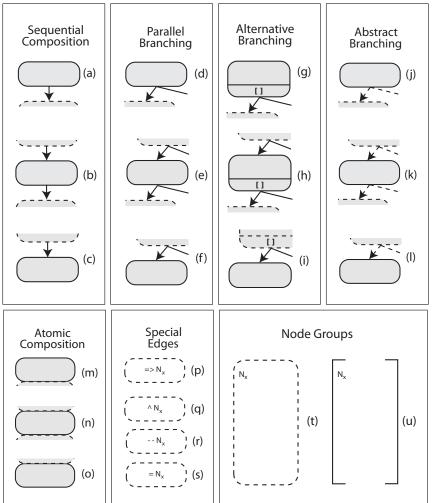

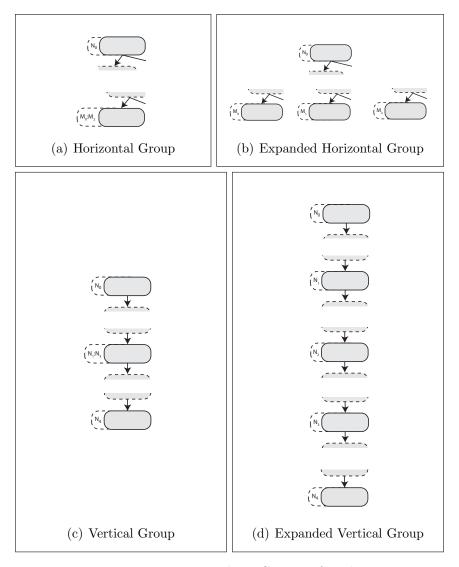

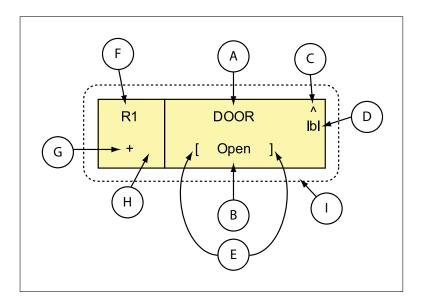

| 3.2  | Summary of the Core Elements of the Behavior Tree Notation     | 61 |

| 3.3  | Behavior Tree Node Naming Conventions                          | 62 |

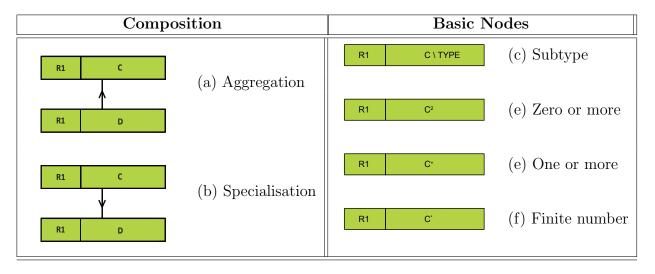

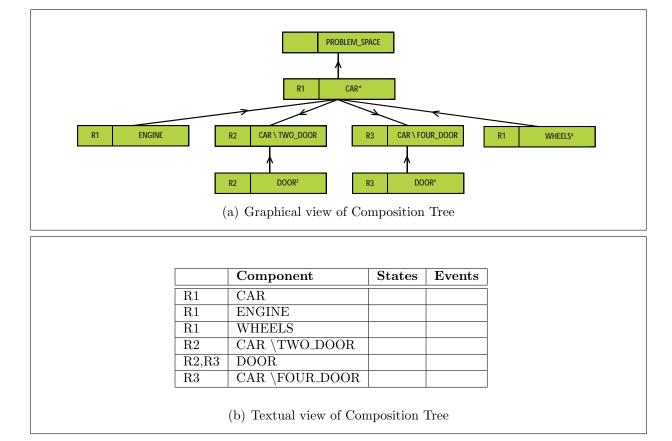

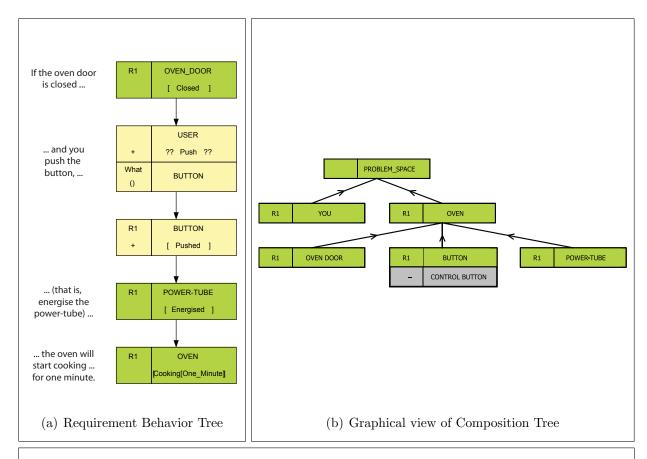

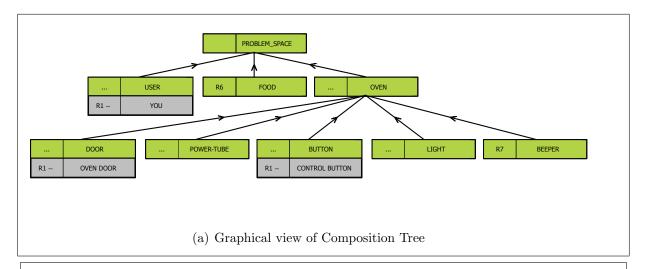

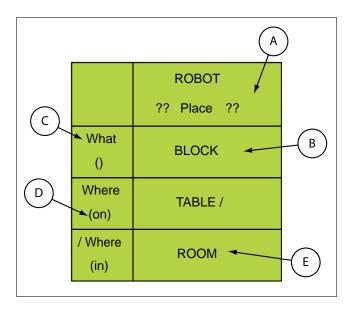

| 3.4  | Summary of the Core Elements of the Composition Tree Notation  | 66 |

| 3.5  | Example Composition Tree                                       | 68 |

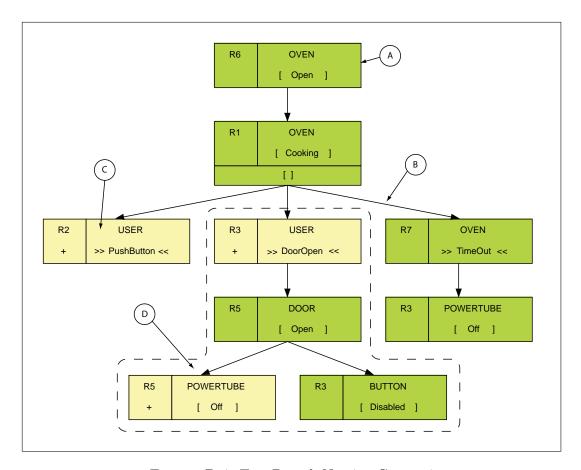

| 3.6  | Initial Translation of Requirement #1 of the Microwave Oven    | 77 |

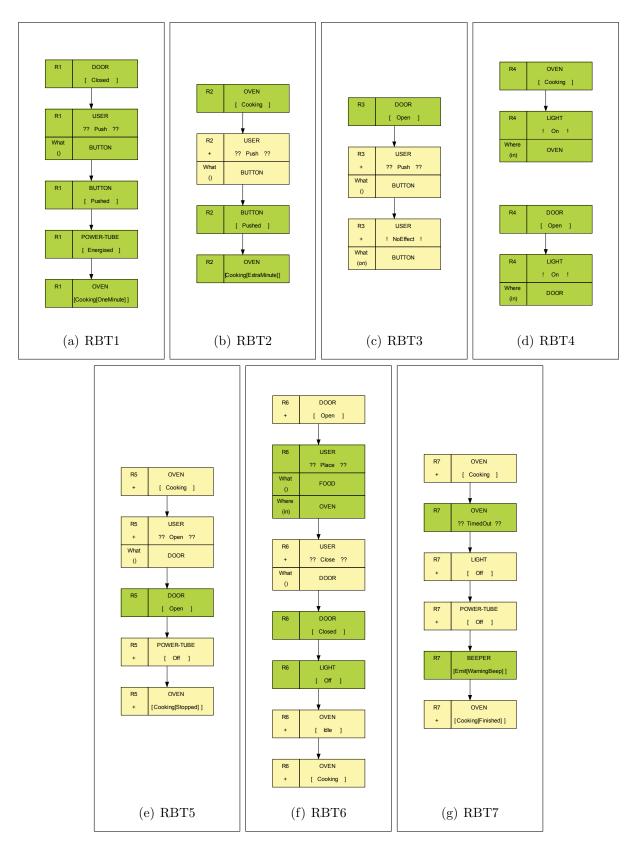

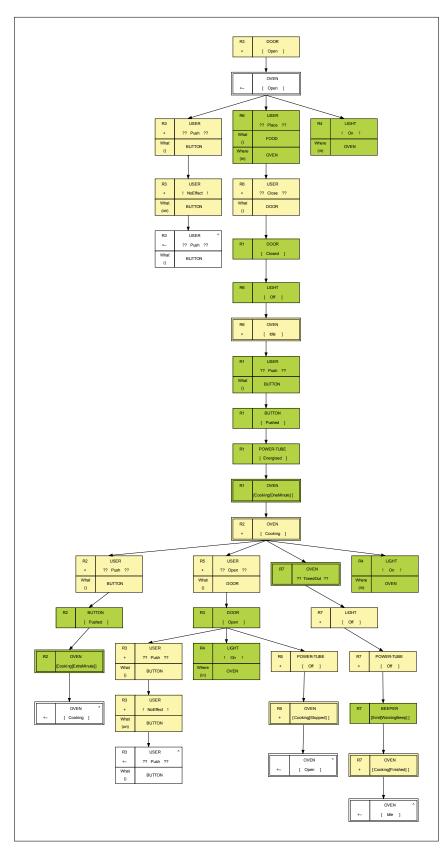

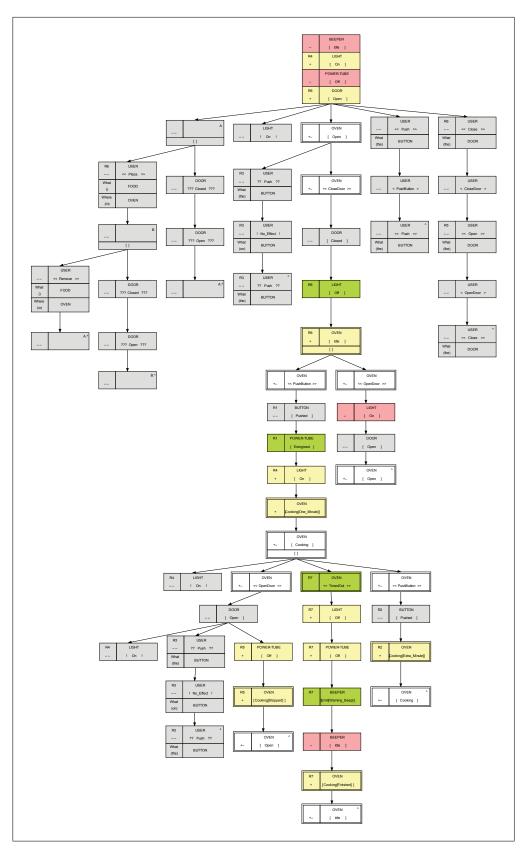

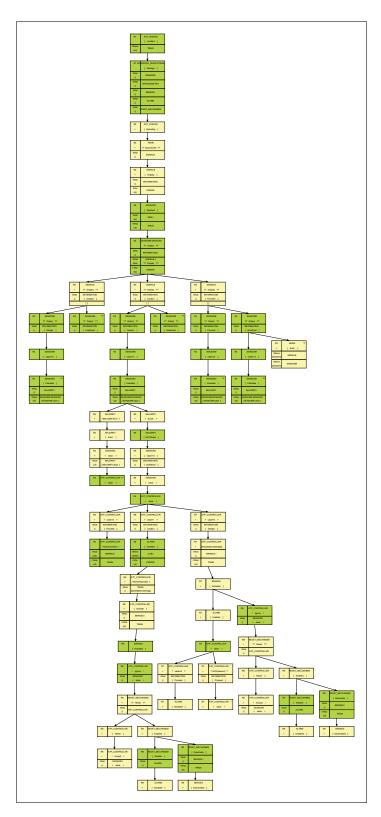

| 3.7  | The Requirement Behavior Trees of the Microwave Oven           | 80 |

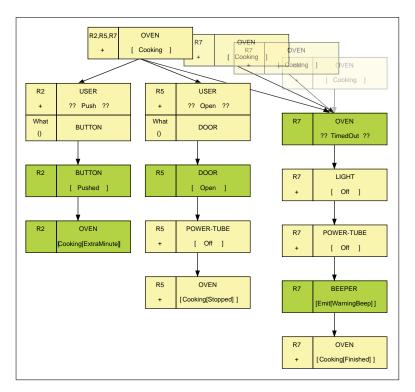

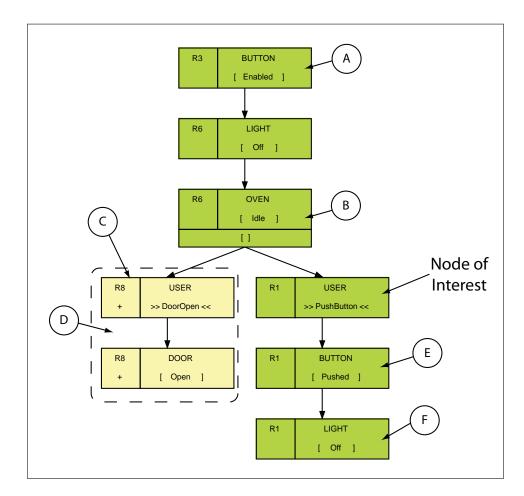

| 3.8  | Integrating RBT2 and RBT5 and integrating the result with RBT7 | 81 |

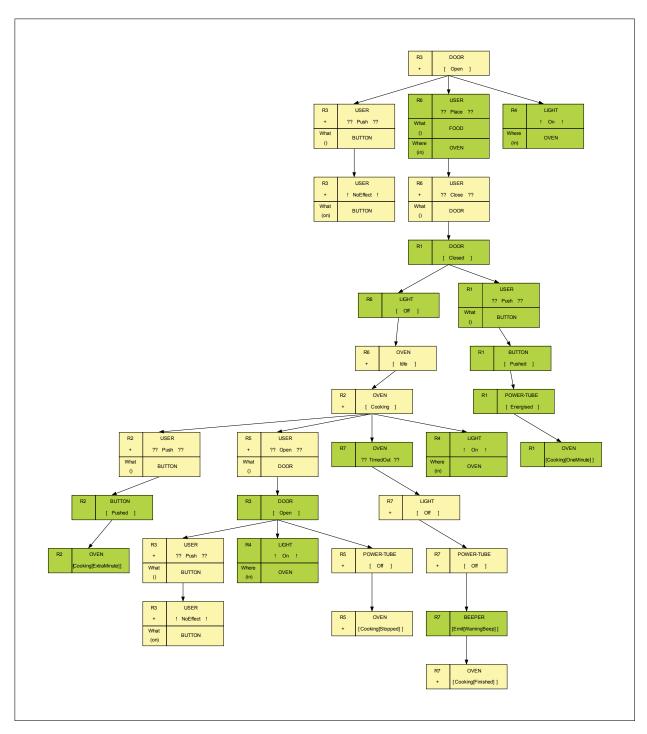

| 3.9  | The Integrated Behavior Tree of the Microwave Oven             | 82 |

| 3.10 | The Integrated Composition Tree of the One-minute Microwaver   | 83 |

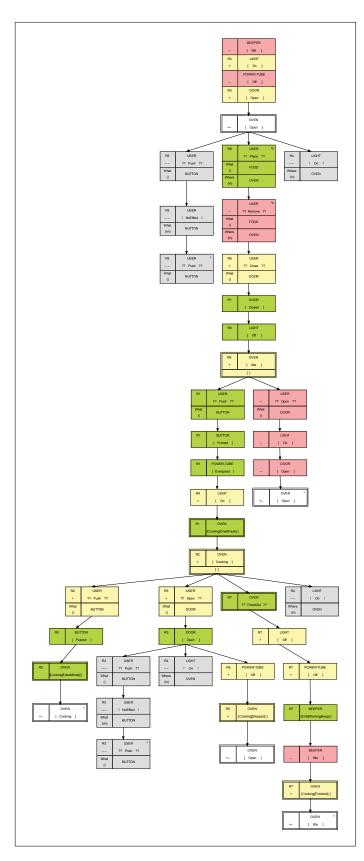

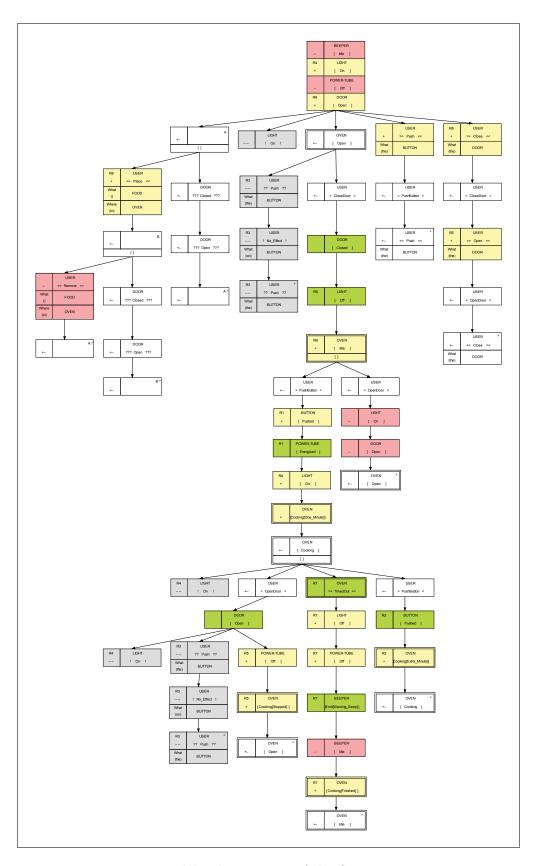

| 3.11 | Partial Model Behavior Tree #1                                 | 85 |

| 3.12 | Partial Model Behavior Tree #2                                 | 87 |

| 3.13 | Model Behavior Tree of the One-minute Microwaver               | 89 |

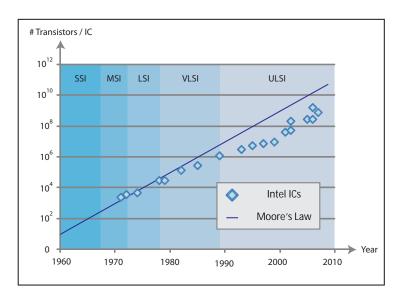

| 4.1  | Exponential Growth of Transistors per Integrated Circuit       | 98 |

XX LIST OF FIGURES

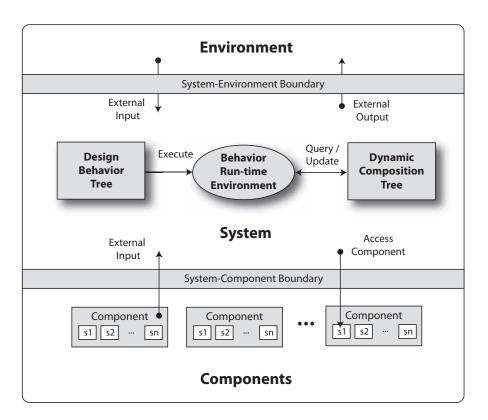

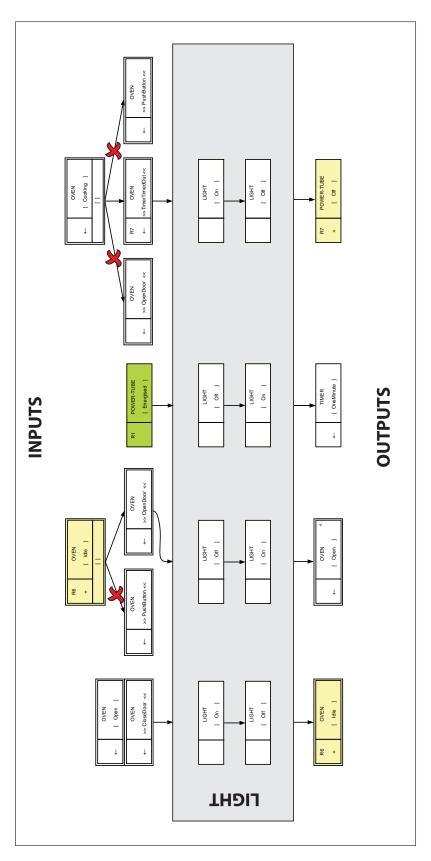

| 4.2  | The structure of a deployed BE system                                              | 100 |

|------|------------------------------------------------------------------------------------|-----|

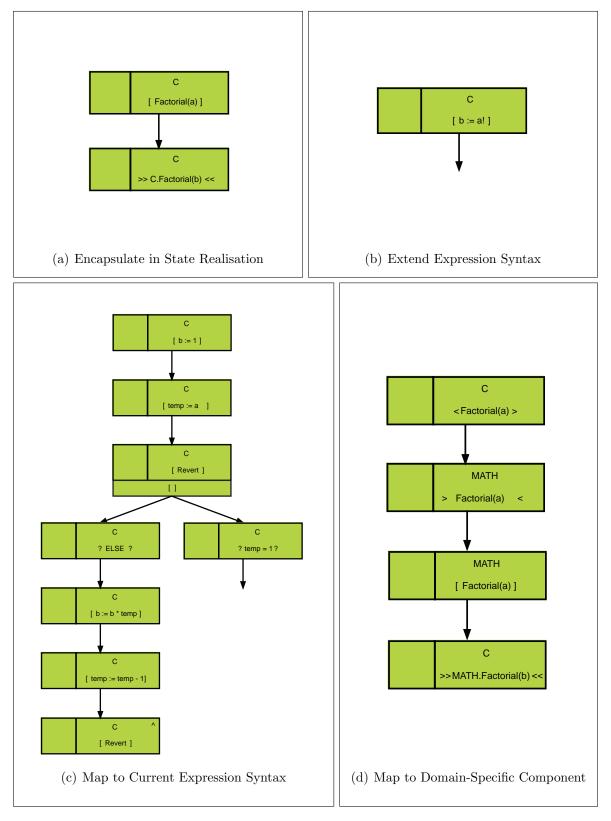

| 4.3  | Extending BT Expression Syntax to include a Factorial Operation                    | 104 |

| 4.4  | Partial Design Behavior Tree #1                                                    | 110 |

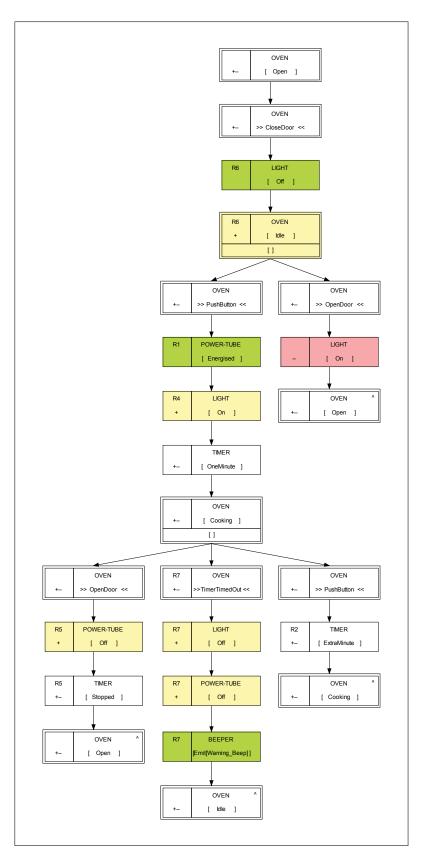

| 4.5  | Design Behavior Tree (with deleted nodes hidden)                                   | 111 |

| 4.6  | An Example Component Interaction Network (CIN)                                     | 112 |

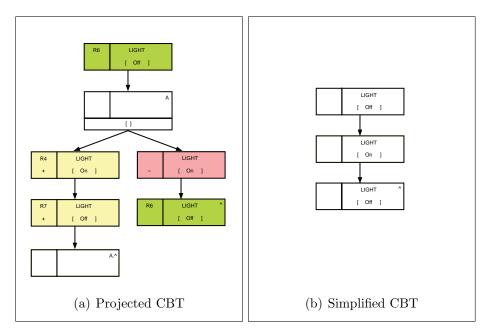

| 4.7  | The Component Behavior Tree (CBT) of the Light Component                           | 113 |

| 4.8  | The Component Interface Diagram (CID) of the Light Component                       | 114 |

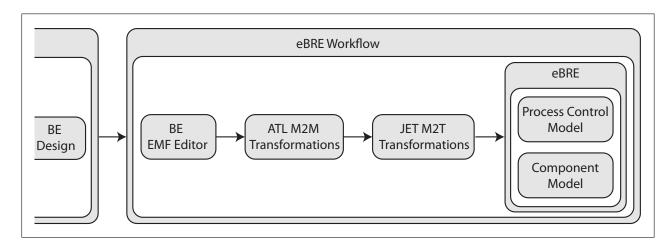

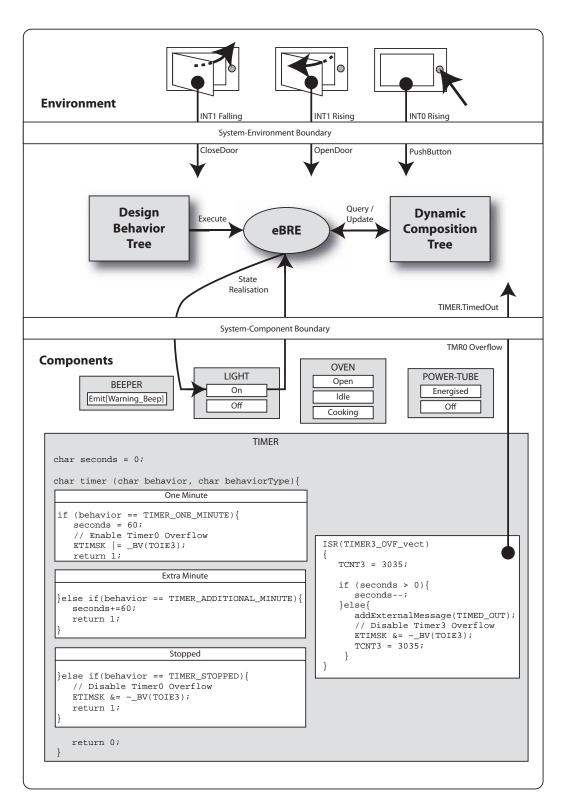

| 5.1  | The workflow of the embedded Behavior Runtime Environment                          | 125 |

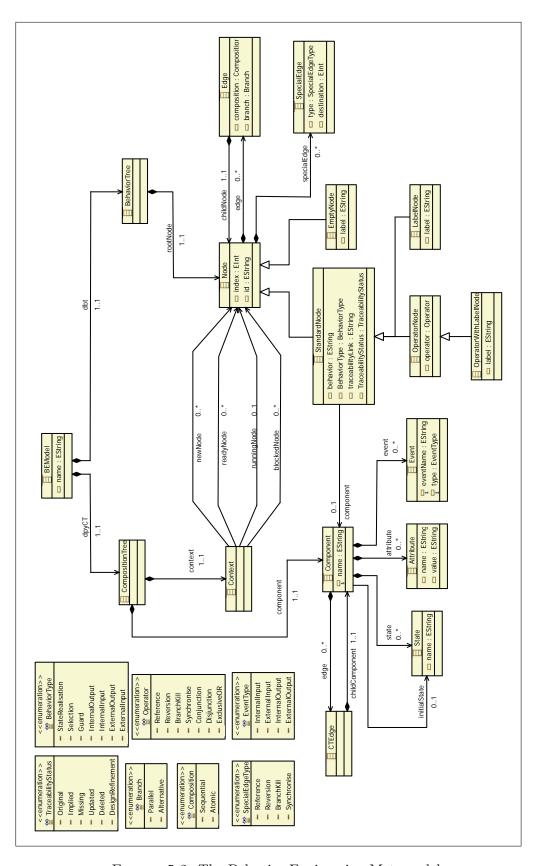

| 5.2  | The Behavior Engineering Metamodel                                                 | 127 |

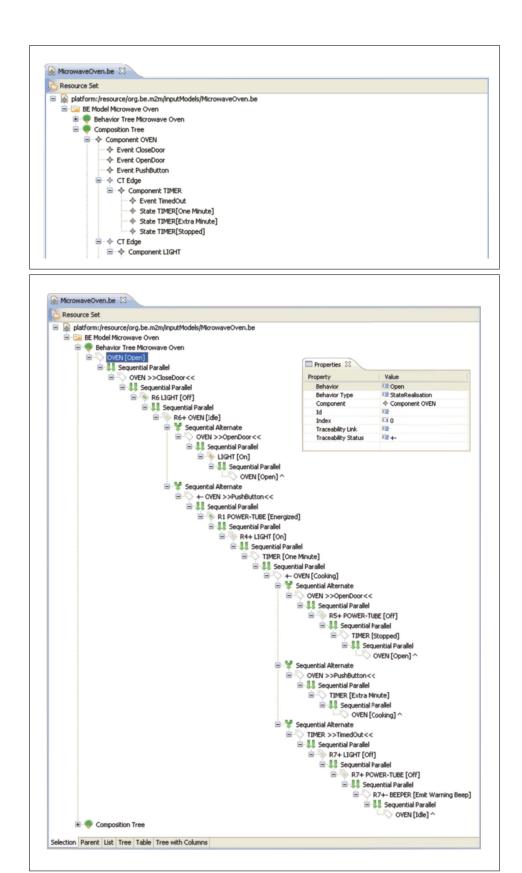

| 5.3  | The BT and CT of the Microwave Oven in the BE EMF Editor                           | 129 |

| 5.4  | Textual Terms for Matching BT Nodes                                                | 131 |

| 5.5  | Graphical Notation for Matching BT Nodes                                           | 132 |

| 5.6  | Matching Groups of Nodes                                                           | 133 |

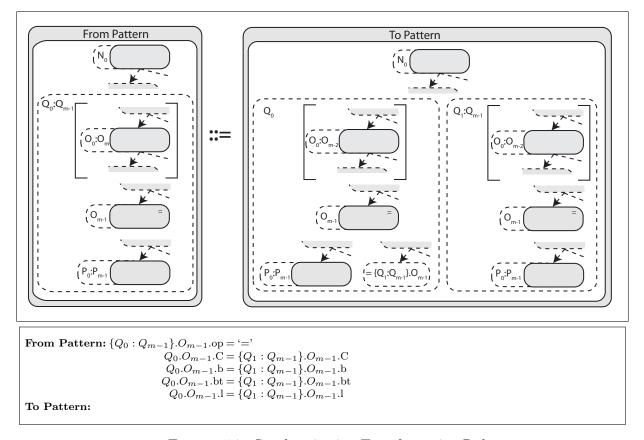

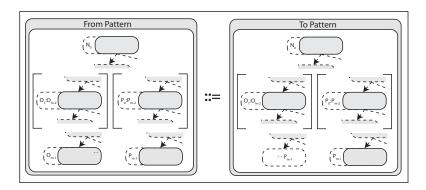

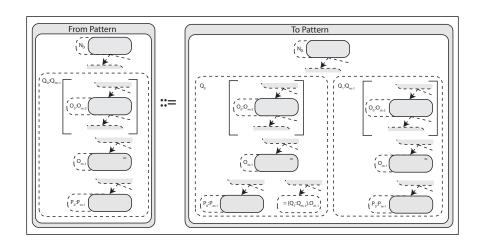

| 5.7  | Synchronisation Transformation Rule                                                | 135 |

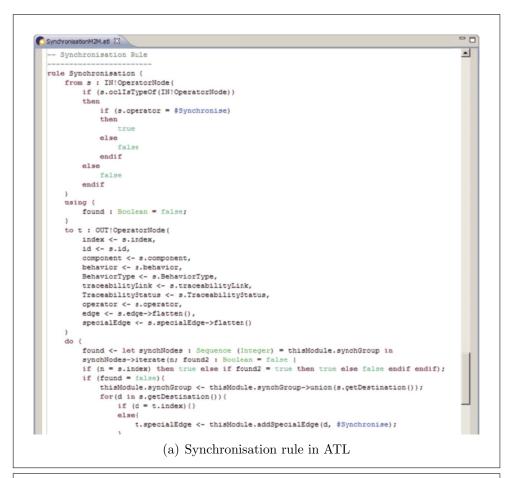

| 5.8  | Implementing the Synchronisation Rule                                              | 136 |

| 5.9  | Generating Code with Java Emitter Templates (JET)                                  | 138 |

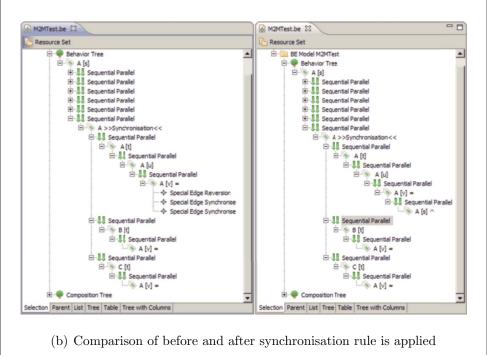

| 5.10 | Code Representation of a Behavior Tree                                             | 139 |

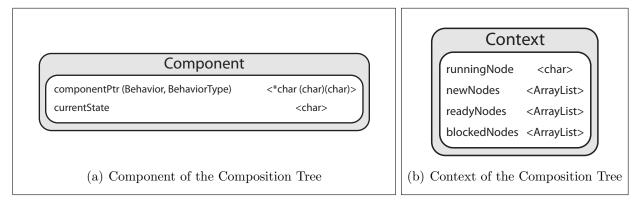

| 5.11 | Code Representation of a Composition Tree                                          | 139 |

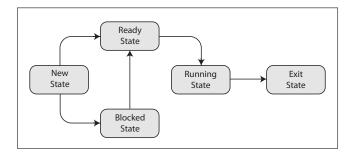

| 5.12 | The Five-State Process Control Model                                               | 140 |

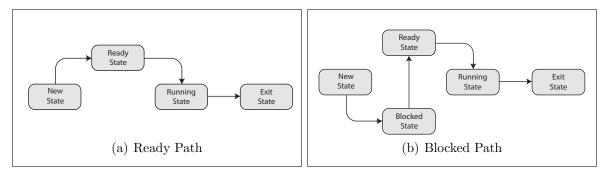

| 5.13 | The two possible paths for a BT Node through the process control model             | 141 |

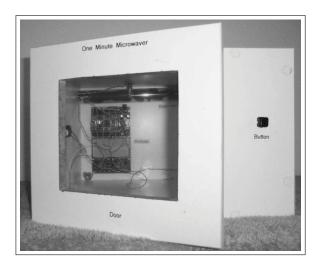

| 5.14 | The BE One-Minute Microwaver                                                       | 144 |

| 5.15 | BE Boundaries of the One Minute Microwaver                                         | 146 |

| 6.1  | From Co-design to Co-modeling                                                      | 158 |

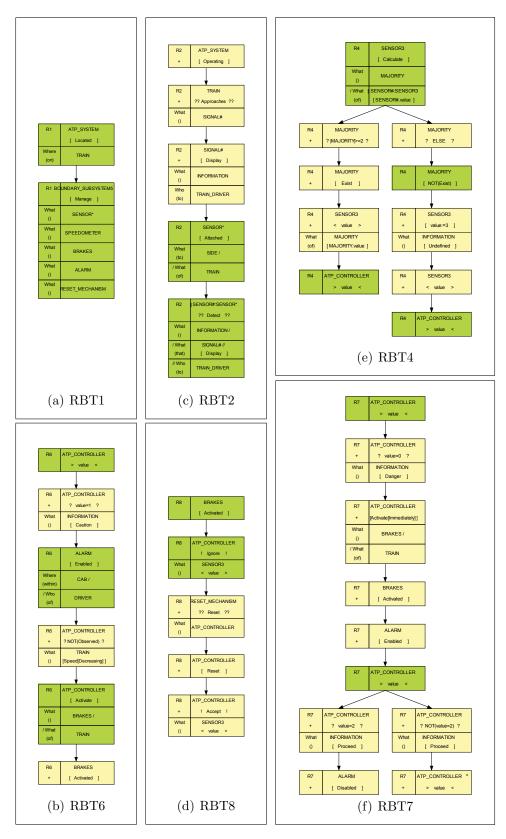

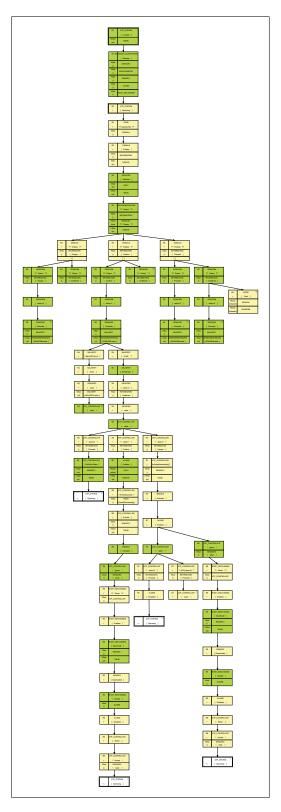

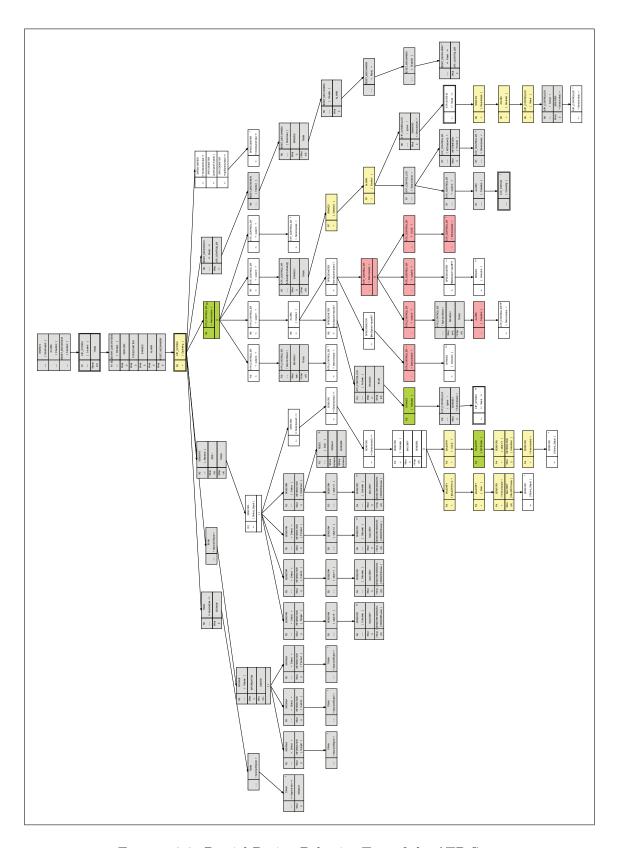

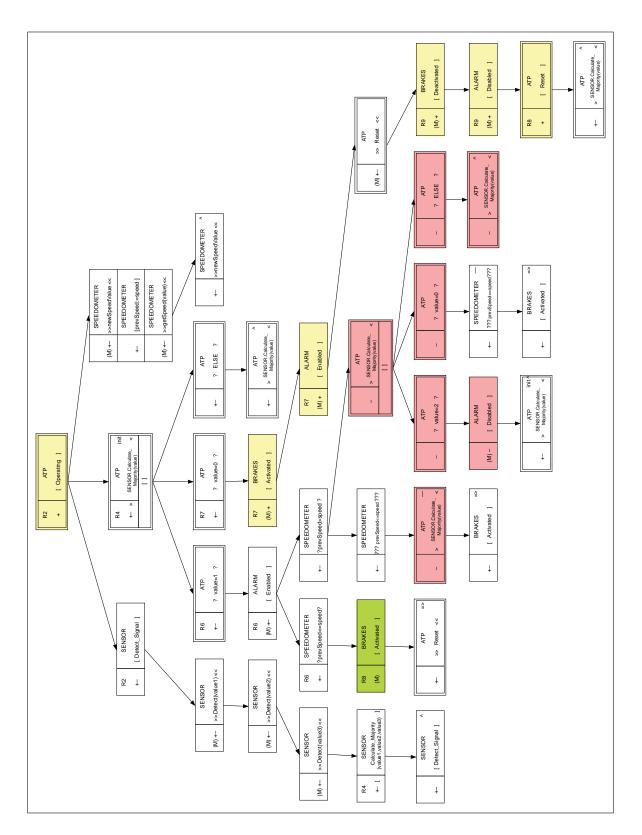

| 6.2  | The Requirement Behavior Trees of the ATP System $(R1,\!R2,\!R4,\!R6,\!R7,\!R8)$ . | 161 |

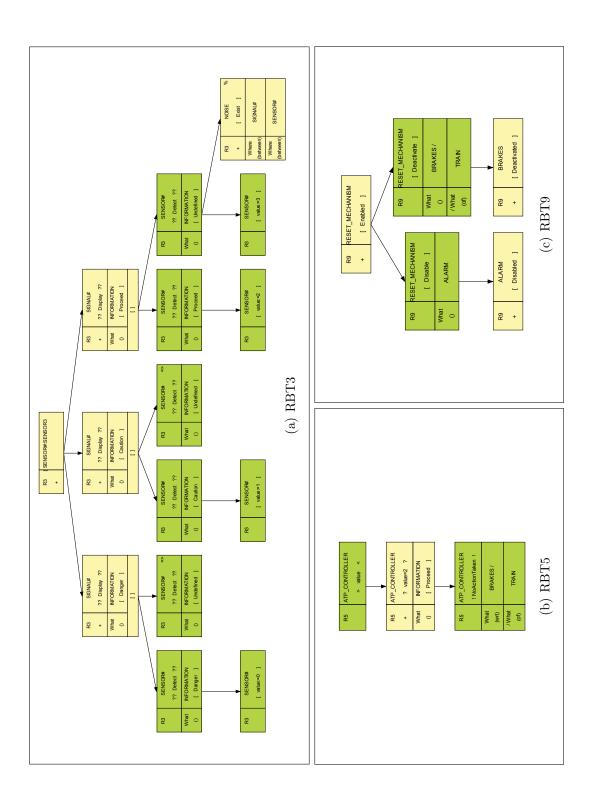

| 6.3  | The Requirement Behavior Trees of the ATP System (R3,R5,R9)                        | 162 |

| 6.4  | The Integrated Behavior Tree of the ATP System                                     | 164 |

| 6.5  | The Integrated Composition Tree of the ATP System                                  | 165 |

| 6.6  | Partial Model Behavior Tree #1 of the ATP System                                   | 167 |

| 6.7  | Partial Model Behavior Tree #2 of the ATP System                                   | 169 |

List of Figures xxi

| 6.8  | Model Behavior Tree of the ATP System                                          | 171 |

|------|--------------------------------------------------------------------------------|-----|

| 6.9  | Partial Design Behavior Tree of the ATP System                                 | 173 |

| 6.10 | Design Behavior Tree of the ATP System (with deleted nodes hidden)             | 176 |

| 6.11 | Component Diagram of the Modelica model of the ATP System                      | 178 |

| 6.12 | Interactions between Modelica and BE Models                                    | 179 |

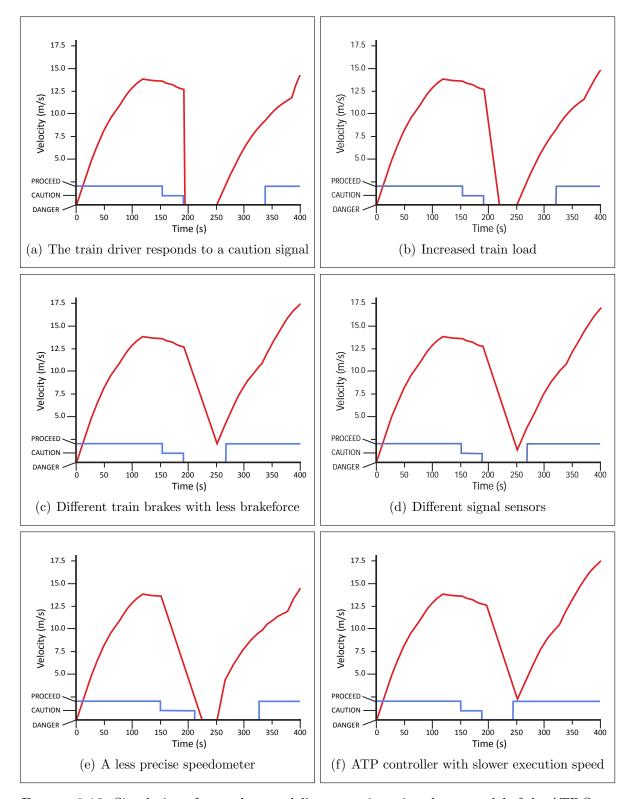

| 6.13 | Simulation of several co-modeling scenarios using the co-model of the ATP      |     |

|      | System                                                                         | 184 |

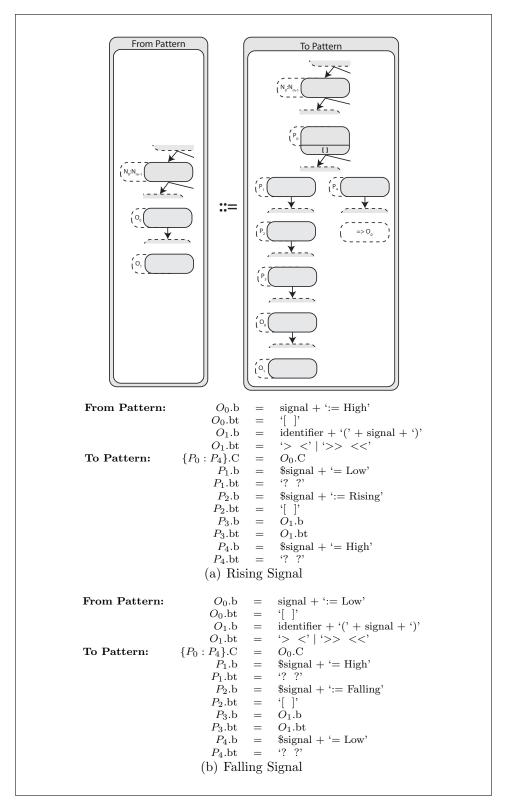

| 7.1  | Mapping for Generating a Rising and Falling Signal State                       | 197 |

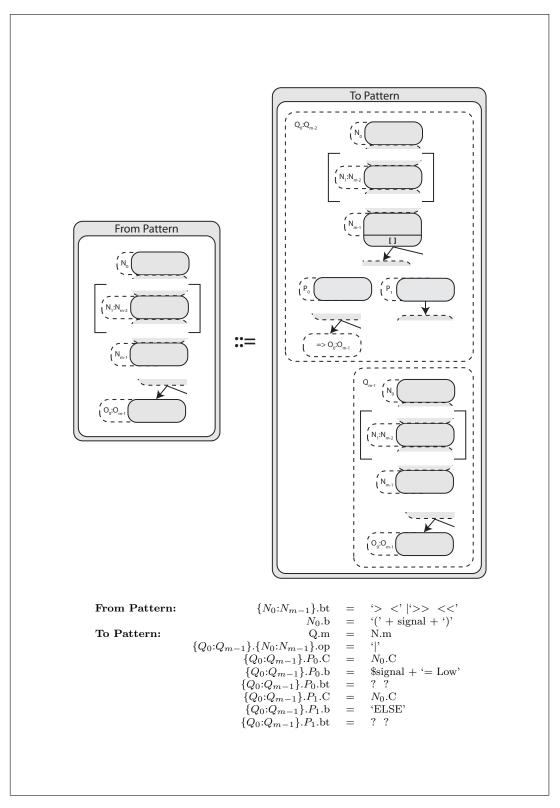

| 7.2  | Mapping for Receiving a Signal from Multiple Sources                           | 198 |

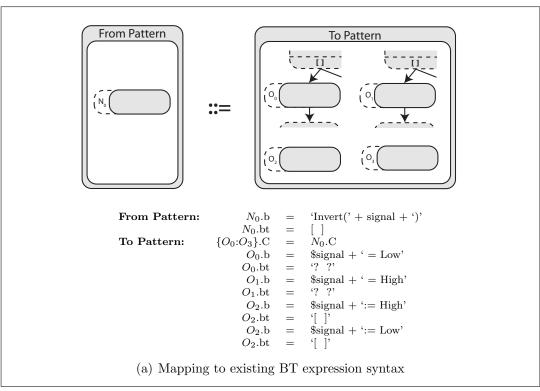

| 7.3  | Two Mappings for Inverting a Signal                                            | 199 |

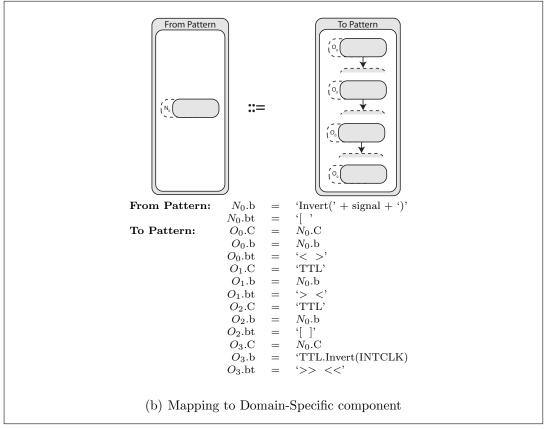

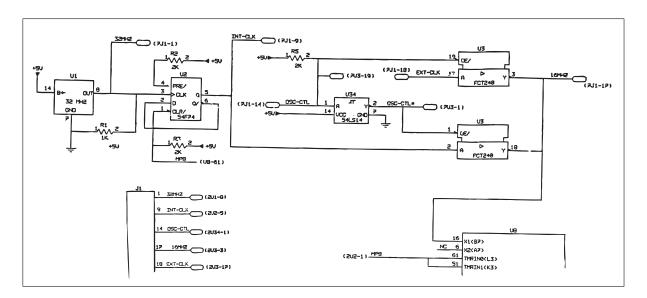

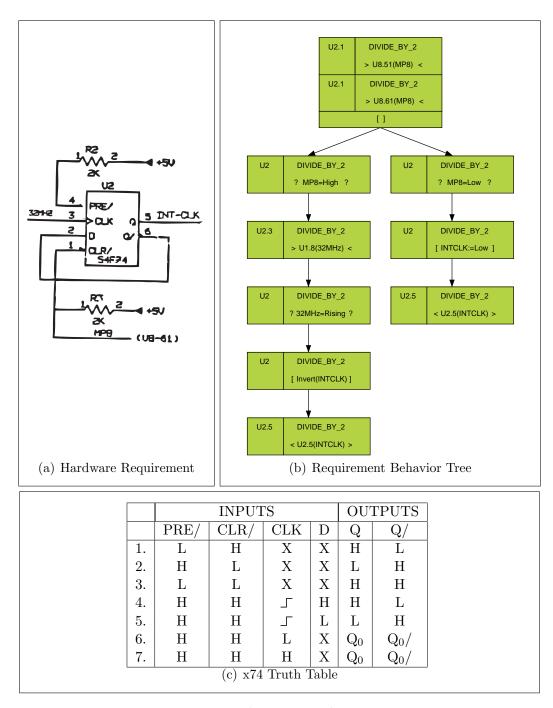

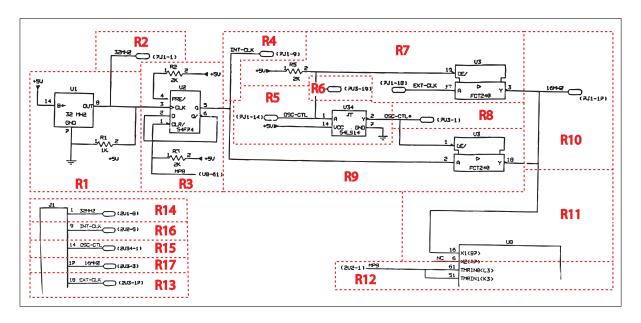

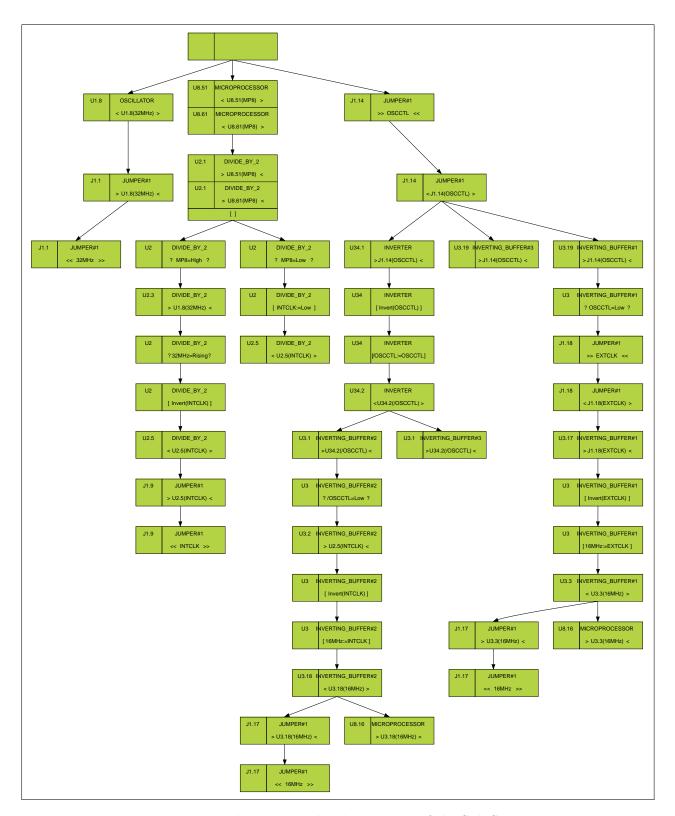

| 7.4  | The Sub-System of the A2 Controller Card                                       | 201 |

| 7.5  | Translating a Hardware Requirement                                             | 202 |

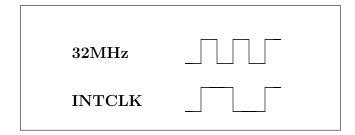

| 7.6  | Comparison of INTCLK and 32MHz signals                                         | 205 |

| 7.7  | The A2 sub-system partitioned into the 17 hardware requirements                | 206 |

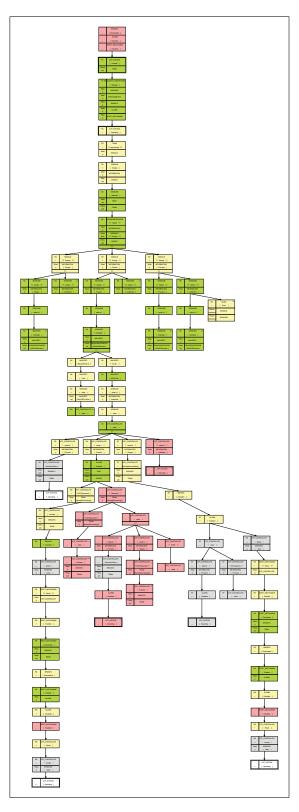

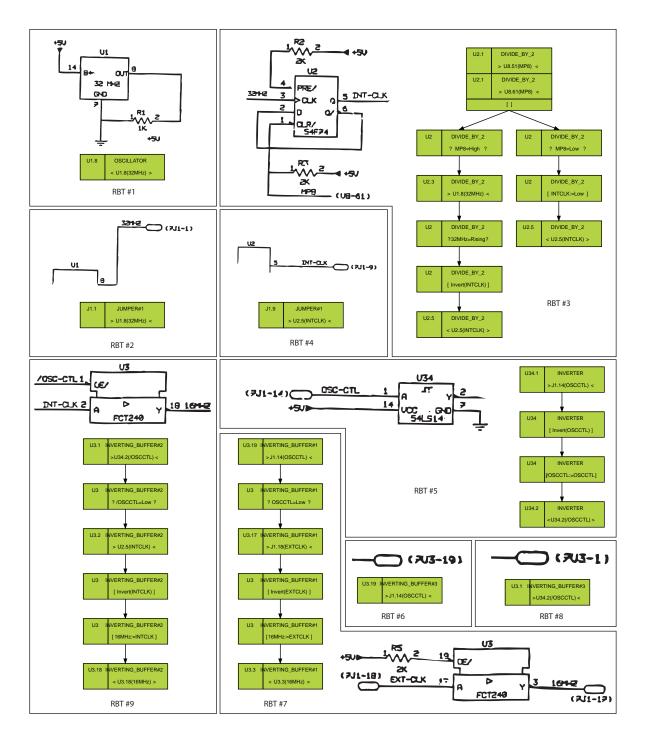

| 7.8  | The Requirement Behavior Trees of the Sub-System (R1-R9)                       | 207 |

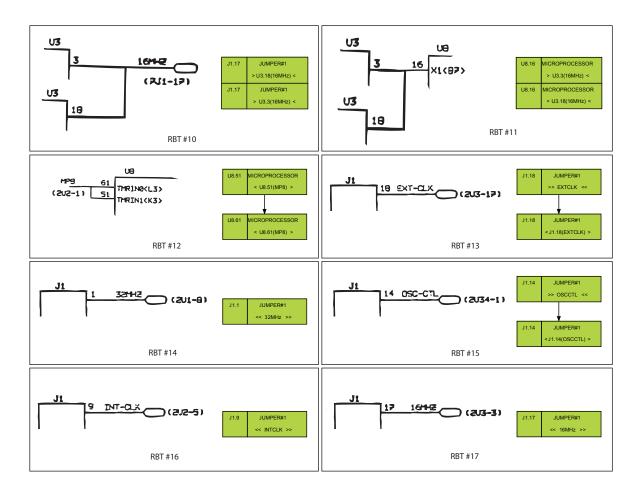

| 7.9  | The Requirement Behavior Trees of the Sub-System (R10-R17)                     | 208 |

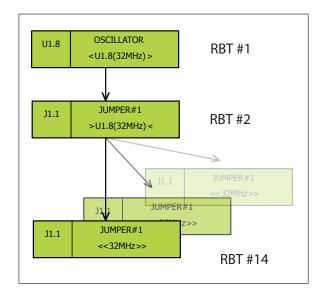

| 7.10 | Integrating RBT1 with RBT2 followed by integration with RBT14                  | 208 |

| 7.11 | The Integrated Behavior Tree of the Sub-System                                 | 209 |

| 7.12 | The Model Behavior Tree of the Sub-System                                      | 213 |

| 7.13 | The Design Behavior Tree of the Sub-System (with deleted nodes hidden) . $\ .$ | 214 |

| 7.14 | The Modified MBT used for Model-Checking                                       | 216 |

| 7.15 | VHDL Code generated from the DBT                                               | 221 |

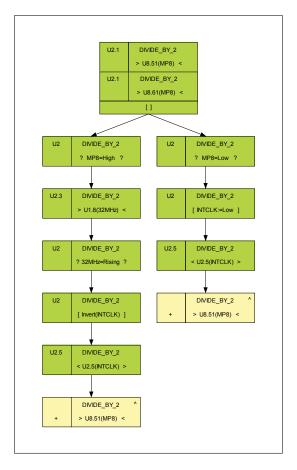

| 7.16 | Component Behavior Tree of Divide By 2 Component                               | 223 |

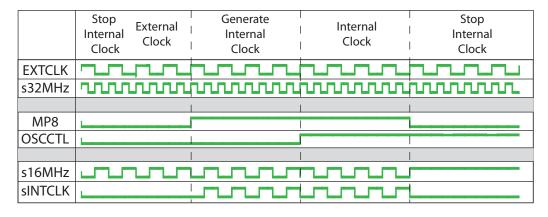

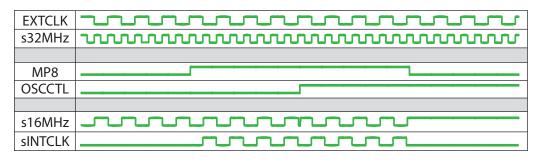

| 7.17 | Simulation of the Clock Select System                                          | 224 |

| 7.18 | VHDL of TTL Version of the Clock Select System                                 | 226 |

| 7.19 | Synthesised Gate-Level design of Clock Select System                           | 227 |

| 8.1  | Summary of Contribution                                                        | 238 |

| A.1  | State Transition Diagram                                                       | 247 |

xxii List of Figures

| A.2  | StateChart of an Aircraft                                                            | 251 |

|------|--------------------------------------------------------------------------------------|-----|

| A.3  | Aircraft StateChart modified to show interdependencies                               | 252 |

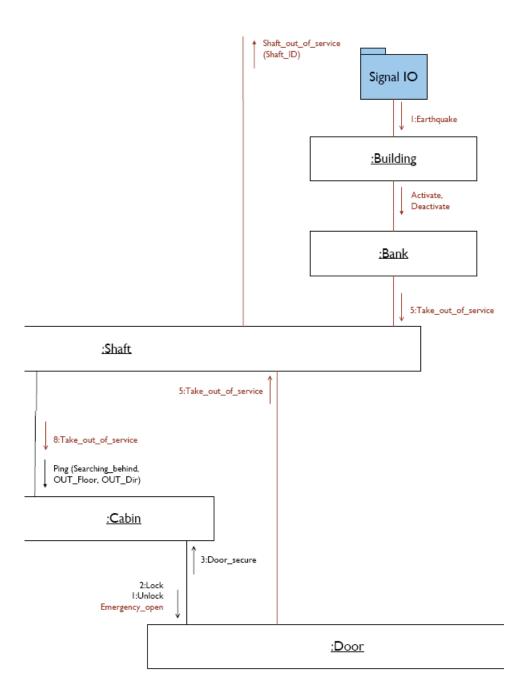

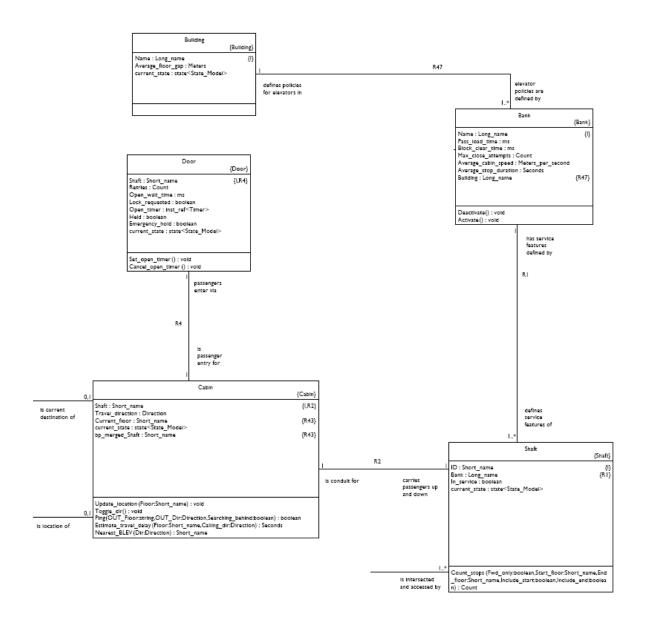

| A.4  | Partial Class Collaboration Diagram                                                  | 255 |

| A.5  | Partial Class Diagram                                                                | 256 |

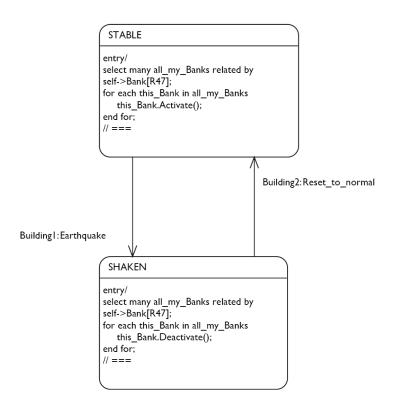

| A.6  | Partial Building StateChart                                                          | 257 |

| A.7  | Partial Bank Operations in Action Language                                           | 257 |

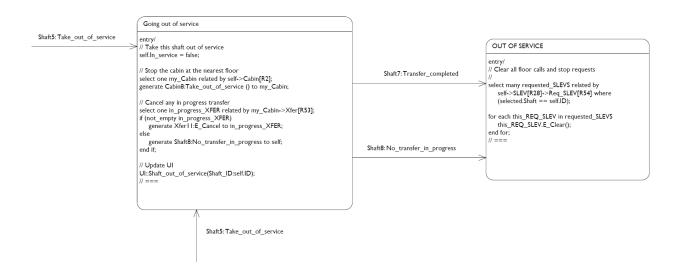

| A.8  | Partial Shaft StateChart                                                             | 258 |

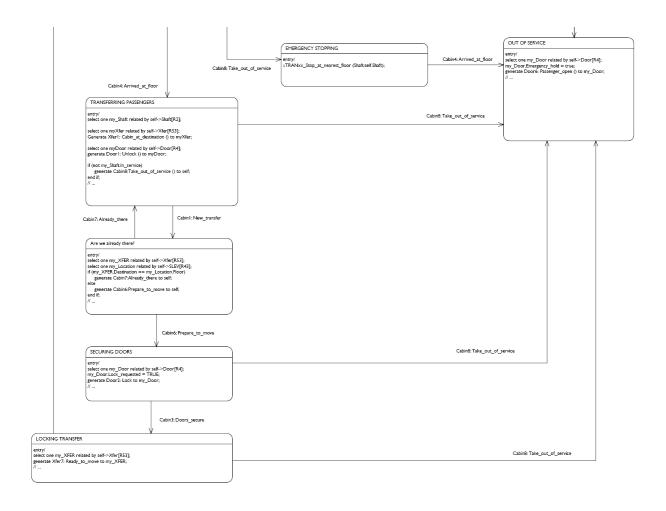

| A.9  | Partial Cab StateChart                                                               | 258 |

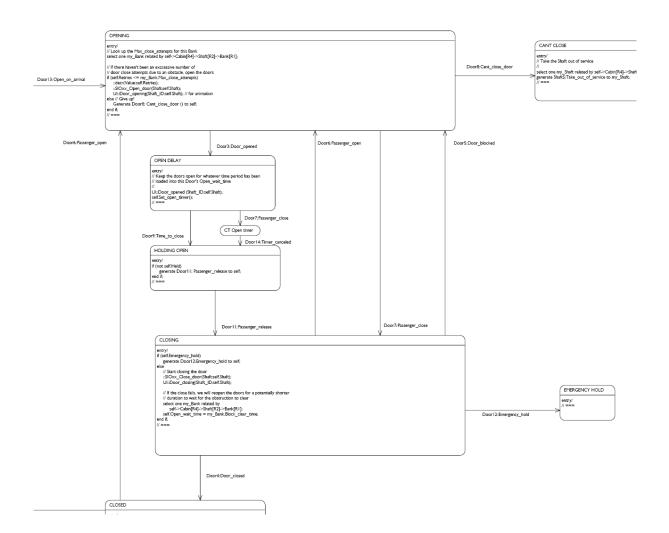

| A.10 | Partial Door StateChart                                                              | 259 |

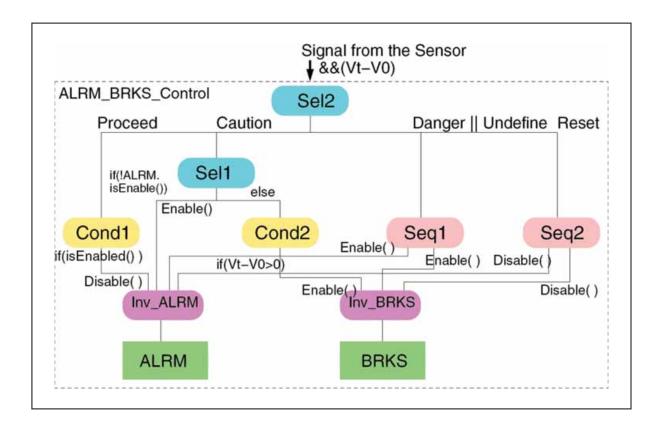

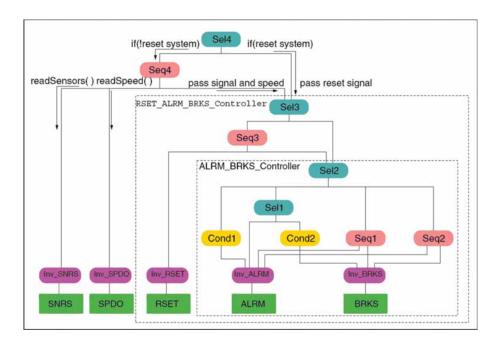

| A.11 | Exogenous Connectors Composite Component Alarm_Brakes_Control                        | 261 |

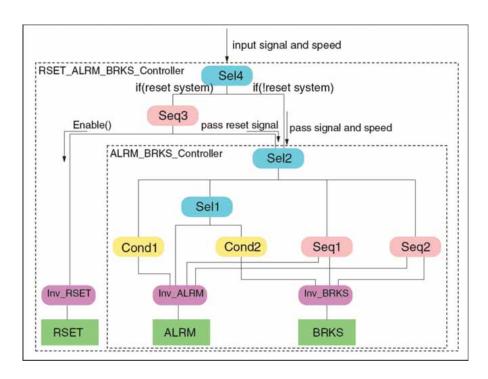

| A.12 | EInterface Definition of ALRM_BRKS_Control Composite Component                       | 262 |

| A.13 | Exogenous Connectors Composite Component Reset_Alarm_Brakes_Control .                | 265 |

| A.14 | Exogenous Connectors model of the Automated Train Protection System                  | 265 |

| B.1  | Behavior Tree Node Naming Conventions                                                | 269 |

| B.2  | Behavior Tree Relation Naming Conventions                                            | 270 |

| В.3  | Behavior Tree Tree Naming Conventions                                                | 271 |

| B.4  | Tree Branch Naming Convention                                                        | 272 |

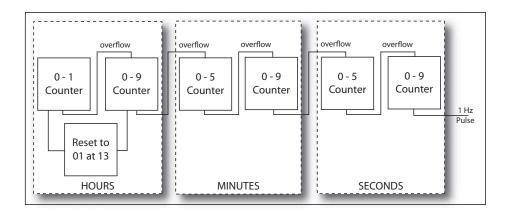

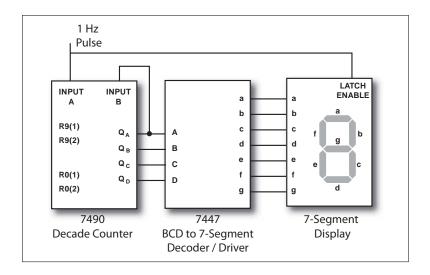

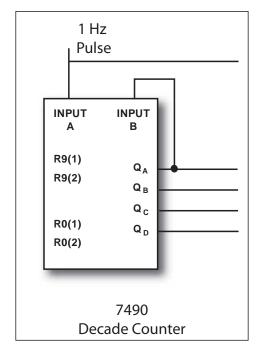

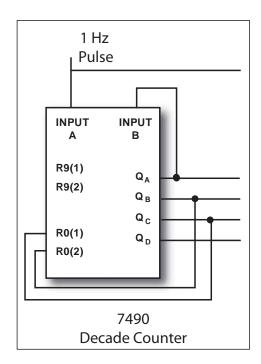

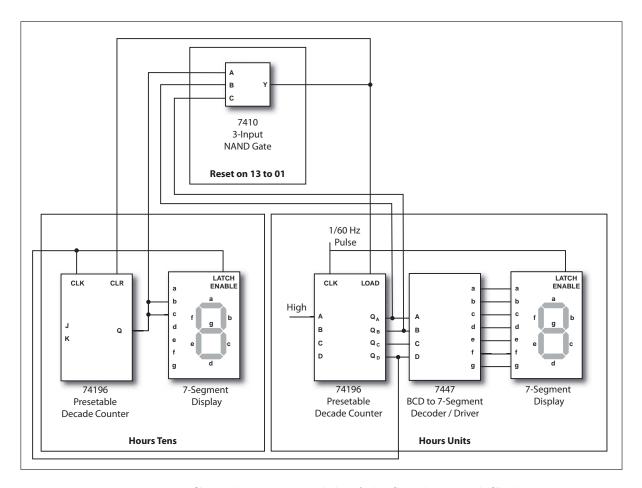

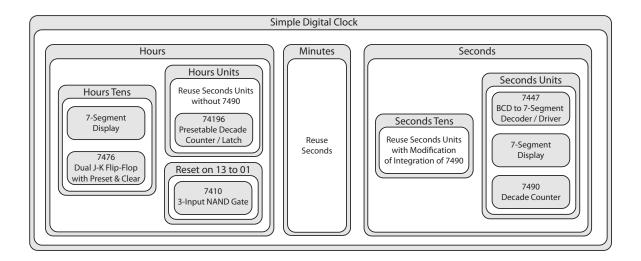

| C.1  | Overview of a simple Digital Clock                                                   | 278 |

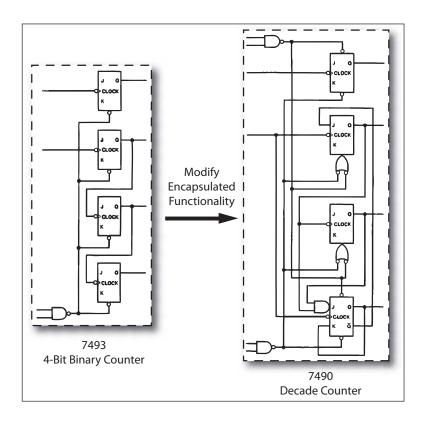

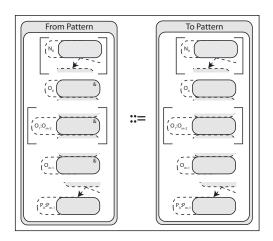

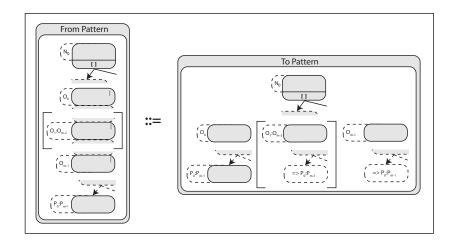

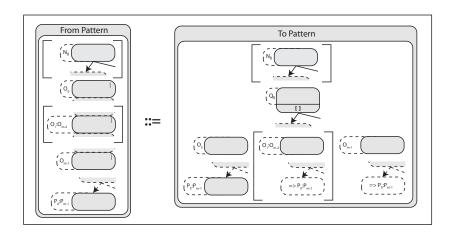

| C.2  | Modifying the Encapsulated Functionality of a Hardware Component $\ \ldots \ \ldots$ | 279 |

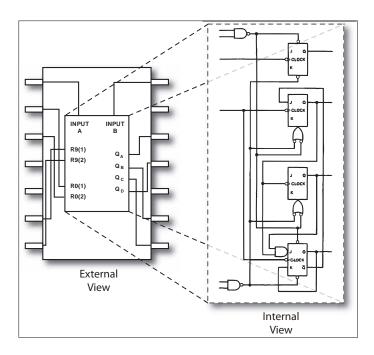

| C.3  | Internal and External Views of the 7490 IC                                           | 280 |

| C.4  | Units of the Seconds Section                                                         | 280 |

| C.5  | Reconfiguring a component using integration                                          | 282 |

| C.6  | The Hours Module of the Simple Digital Clock                                         | 283 |

| C.7  | Reuse in Digital Clock Case Study                                                    | 284 |

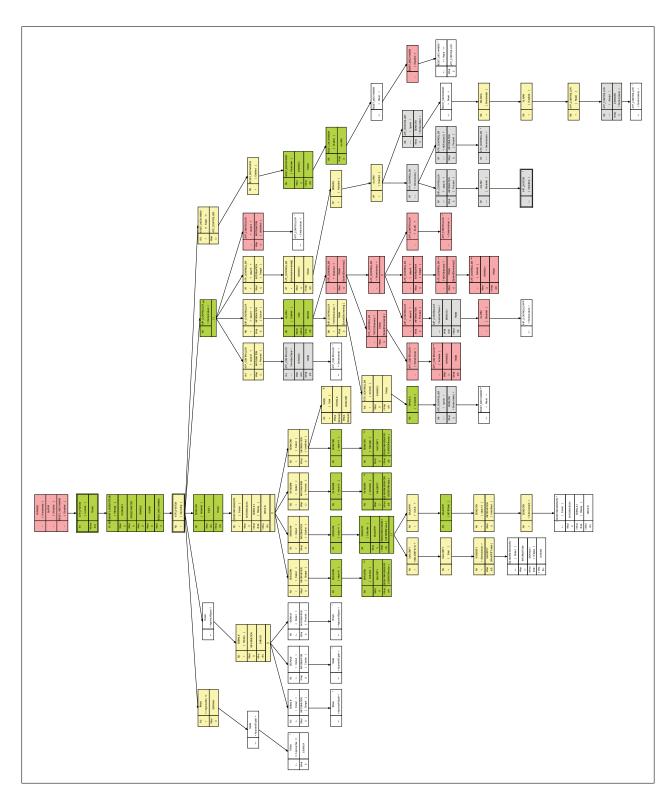

| D.1  | Conjunction Transformation Rule                                                      | 286 |

| D.2  | Disjunction Transformation Rule (Alternate Branching)                                | 287 |

| D.3  | Disjunction Transformation Rule (Parallel Branching)                                 | 287 |

| D.4  | Exclusive OR Transformation Rule (Alternate Branching)                               | 288 |

List of Figures xxiii

| D.5 | Exclusive OR Transformation Rule (Parallel Branching) | 288 |

|-----|-------------------------------------------------------|-----|

| D.6 | Reversion Transformation Rule                         | 289 |

| D.7 | Reference Transformation Rule                         | 289 |

| D.8 | Branch-Kill Transformation Rule                       | 290 |

| D.9 | Synchronisation Transformation Rule                   | 290 |

xxiv List of Figures

## List of Tables

| 2.1 | Summary of Behavior-Based Approaches                                         | 41  |

|-----|------------------------------------------------------------------------------|-----|

| 3.1 | Summary of the first three stages of the Behavior Modeling Process           | 69  |

| 3.2 | Requirements of the Microwave Oven                                           | 76  |

| 3.3 | Issues found during translation of requirements of the One-minute Microwaver | 79  |

| 4.1 | Comparison of Potential Applications of the BE specification                 | 95  |

| 4.2 | Hardware Components versus BE Components                                     | 99  |

| 5.1 | 2003 and 2008 Embedded Systems Development Survey Results                    | 122 |

| 5.2 | The Behavior of BT nodes through the Process Control Model                   | 142 |

| 5.3 | Order of operation of the process control model                              | 143 |

| 6.1 | Requirements of the ATP system                                               | 160 |

| 6.2 | Issues found during translation of requirements of the ATP System            | 163 |

| 7.1 | Three approaches to dealing with Legacy systems                              | 193 |

| 7.2 | Mapping VHDL functionality to Behavior Trees                                 | 195 |

| 7.3 | Results of Performing Failure Modes and Effects Analysis                     | 219 |

| A.1 | State Transition Table                                                       | 248 |

| A.2 |                                                                              | 260 |

| B.1 | Variable Naming Conventions                                                  | 268 |

xxvi List of Tables

| B.2 | Elements of a Behavior Tree Node     | 269 |

|-----|--------------------------------------|-----|

| В.3 | Elements of a Behavior Tree Relation | 270 |

| B.4 | Nodes of a Behavior Tree             | 271 |

| R 5 | Branches of a Behavior Tree          | 272 |

#### Supplementary Material

This dissertation is accompanied by supplementary material in the form of electronic resources included on an accompanying compact disc. Inserting the compact disc into your computer should automatically open a page in your web browser with links to access the electronic resources. If the page fails to open, the folder structure can be browsed manually. The folder structure and contents of the electronics resources are as follows:

- Case Studies: Electronic versions of all work products of the three case studies in the dissertation in Portable Document Format (PDF).

- Microwave Oven

- Automated Train Protection System

- Clock Selector

- Behavior Tree Traces: Animated traces demonstrating the semantics of the Behavior Tree language in the Scaleable Vector Graphics (SVG) format. The SVG files should display in most web browsers.

- Basic Nodes

- Composition

- Operators

- Author's Publications: The publications of the author in Portable Document Format (PDF).

# Part I Introduction & Background

Introduction

Marketplace demand is driving the need to develop software-intensive systems of ever increasing scale and to deliver products in shorter time frames, for less cost, and of a higher quality. Managing the complexity created by the increasing scale of these systems is crucial, as it impacts upon the related factors of time, cost and quality. Despite this, mainstream approaches to software and systems engineering (Sw&SE) do not adequately address the issue of scaleability.

If scaleability is not adequately addressed, it can play havoc with even the most simple tasks. This is easily demonstrated by contrasting a mental arithmetic approach to solving an arithmetic problems with a paper-and-pencil approach. The sum of two 2-digit numbers (e.g. 39 + 54) can be easily computed using either of the two approaches. The sum of two 7-digit numbers (e.g. 3452938 + 1295729), however, is much more difficult to solve using

4 Introduction

mental arithmetic than using a paper-and-pencil approach. Finally, it is almost impossible for most people to compute the sum of five 7-digit numbers mentally whilst it still remains easily solvable using a paper-and-pencil approach.

The larger scale summations remain solvable with paper-and-pencil because partial results can be recorded on paper. This means the final result can be calculated by repeatedly adding two digits at a time. The paper-and-pencil approach is scaleable in essence because the *local problem space* (adding two digits) remains constant regardless of the *global problem space* (adding two or more numbers). Mental arithmetic does not scale because partial results form part of the local problem space, thereby causing an increase in the global problem space to also result in an increase in the local problem space. The increasing size of the local problem space leads to an overload of the short-term memory because the partial results have to be remembered whilst also trying to calculate the addition of two digits.

Approaches to Sw&SE that do not adequately address scaleability are analogous to mental arithmetic in the previous example. It is possible to proceed directly to a formal specification, a design or even a deployed system if one attempts only a small-scale textbook example with only a few requirements as it is possible to resolve many of the issues informally and intuitively. As the scale increases, however, an informal approach to resolving these issues is no longer feasible as the short-term memory is overloaded by the interdependencies of the requirements.

One result of the struggle of mainstream Sw&SE approaches to manage the complexity of large-scale software-intensive systems is widespread failure of projects. Charette [Cha05] estimates that 5-15% of software projects conducted in 2005 failed as a result of either being abandoned before they were finished or just after delivery due to not meeting the needs of the client. Charette also found that large-scale software projects are three to five times more likely to fail than smaller projects. Unless dealt with appropriately, the exponential rise of complexity created by the need to develop software systems of increasing scale will make the failure of large-scale software projects even more commonplace.

There is therefore an obvious need for a Sw&SE methodology which can handle the complexities of developing large-scale systems. A scaleable methodology for Sw&SE must maintain a local problem space of constant size regardless of the global problem space (e.g.

thousands of requirements). This methodology must therefore build a system out of its requirements, using a rigorous approach to translate each requirement individually in a formal and repeatable way until a complete system specification is built. A design that results in the satisfication of the specification requires a similar approach that individually applies design decisions to the specification until a completed design is built. The resulting design can then be used as the basis for a variety of deployed systems. This end-to-end approach of building a system from out of its requirements differs to mainstream Sw&SE approaches which use a miraculous intuitive leap to proceed from the requirements to a specification, a design or a deployed system.

We propose that the reason that mainstream Sw&SE approaches do not adequately address scaleability is that they use representations that prohibit scaleable methodologies. Consider again a paper-and-pencil approach to arithmetic, this time using roman numerals instead of arabic numerals. The task of adding two numbers is now complicated by a mismatch between the representation and a scaleable methodology; since roman numerals are not positional, it is no longer possible to deal with two digits at a time. This mismatch between representation and a scaleable methodology in arithmetic is analogous to mainstream Sw&SE approaches which use representations that do not allow one requirement to be dealt with at a time.

A Sw&SE approach, however, with a representation that enables a scaleable methodology, can dramatically improve our ability to manage the complexity of large-scale systems. By managing this complexity, a scaleable methodology enables systems to be built in shorter time frames, for less cost and to be made at a higher quality.

A scaleable methodology enables shorter timeframes for system delivery by using a divide and conquer approach. Revisiting our arithmetic analogy, if we have 100 numbers to add, one person could perform 99 additions to add the 100 numbers. Alternatively, if ten people add ten numbers each, 90 of these additions can be performed concurrently with the results used to perform the remaining nine additions. Applying this to system design, rather than one person translating 100 requirements it would be possible for ten people to concurrently translate ten requirements each and integrate the results <sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>While this approach would result in a significantly faster translation of the requirements, it requires

6 Introduction

A scaleable methodology reduces project cost by supporting the task of risk analysis to mitigate the possibility of schedule slippage and project failure. Risk analysis is improved because a scaleable methodology provides a clear understanding of the status of the project at all stages of development. This clarity is provided by metrics such as the number of requirements translated and the number of defects found, which provide concrete indicators of the status of project and the projected cost of further development.

A scaleable methodology increases project quality by building a system from out of its requirements. This creates work products that have direct traceability to the original requirements and that preserve the original intent and vocabulary of the system analyst. The formalisation process also increases defect detection, allowing defects to be addressed earlier which results in a higher quality final product.

Although mainstream approaches can also enable shorter timeframes using a divide and conquer approach, the divisions are based upon an informal top-down analysis performed at the early stages of development. A lack of understanding of the system being built at these early stages may result in the system being poorly divided. This in turn can cause problems during integration of the parts or can result in the creation of a substandard design.

The miraculous intuitive leap which is used by conventional approaches to proceed from the requirements to a final work product also has detrimental impacts on the cost and quality of a project. Traceability to the requirements is lost which increases the risk that some requirements will not be addressed. Determining whether requirements are addressed necessitates testing which can only be performed during the later stages of development. Quick iterative cycles of development are then performed to mitigate the risk created by the uncertainty of the project status prior to testing. This iterative approach addresses the risk at the expense of an added cost of development and testing. When defects are eventually located using testing, they are usually discovered later in development when they are more costly to fix.

additional support for the information that is gathered concurrently to be consistent.

#### 1.1 Objective and Approach

The objective of this dissertation is to address the issue of scaleability in Sw&SE by providing the foundations for a scaleable, widely applicable, end-to-end methodology. This dissertation will use these foundations to demonstrate the applicability of the approach and the potential benefits it can provide. It is hoped that demonstrating these potential benefits will encourage further research into this area, providing the critical mass required to create a finalised methodology. This approach of driving methodology development from practical experience is also favored by other researchers that study design ([Ale64], Preface):

"... I think it is absurd to separate the study of designing from the practice of design. In fact, people who study design methods without practicing design are almost always frustrated designers who have no sap in them, who have lost, or never had, the urge to shape things. Such a person will never be able to say anything sensible about "how" to shape things either."

Satisfying the objective of providing the foundations for a scaleable, widely applicable, end-to-end methodology, requires the approach described in this dissertation to have the following characteristics. Firstly, satisfying the objective of providing the foundations for a scaleable methodology requires the approach to begin at the requirements. Then, the local problem space must remain minimised and constant regardless of the global problem size throughout the whole process from the requirements to the final work product. Secondly, to satisfy the objective of an end-to-end methodology, the approach must proceed all the way from the requirements to result in a final work product of a deployed system. This ensures that the approach provides the largest productivity benefits. It also allows the results of the approach to be compared against existing mainstream Sw&SE approaches which result in deployed systems. Thirdly, to satisfy the objective of a widely applicable methodology, the approach must be demonstrated to apply to a wide area of both problem domains and solution domains. This ensures that the effort of creating a scaleable methodology is justified as the benefits of the approach can be widely achieved in numerous areas.

We propose utilizing the Behavior Engineering approach to achieve these objectives rather than independently developing a new approach. Behavior engineering (BE) [Dro06c] is an 8 Introduction

integrated approach to systems development initally proposed by Dromey in 2001 [Dro01]. It supports the engineering of large-scale dependable software intensive systems at both the systems and software engineering level. BE has had significant success in industry where it is currently used primarily for requirements analysis of large specifications [Pow07, Bos08].

The success of BE in requirements analysis is primarily due to using a scaleable methodology that deals with one requirement at a time. BE uses a bottom-up process that enables each requirement to be modeled independently and integrated one at a time to to form a complete view of the system specification that is built out of the requirements. Combining this scaleable methodology with a rigorous approach to translation results in a model complete with traceability back to the original natural language requirements. This scaleable methodology is enabled by BE's graphical representation that visually captures the information in natural-language requirements as the behavior of a system composed of a set of integrated components. The component interactions are formally defined in a multi-threaded language which co-ordinates the individual behaviors associated with each of the components. The separation of computation from integration using components is an approach gaining traction in the research community, as evidenced by several component-based representations [Par00, Arb04, LLW06].

Current research involving BE focuses primarily on using BE models as a formal specification, which can then be further analysed using techniques such as model-checking. An approach to design with BE has been outlined previously by Dromey [Dro06c], but this muddled the creation of a specification with the task of adding real design decisions beyond the specification. This dissertation provides a new approach to design using BE which separates specification and design into separate stages and clarifies the types of design decisions that need to be made to go from a specification to a design in BE.

Another central part of our approach is to develop the new design stage for BE within a model driven engineering (MDE) framework. MDE<sup>2</sup> is a software engineering approach that advocates a shift from code-centric development to model-centric development, in which models are the primary artifacts of all stages of development. Models help manage

<sup>&</sup>lt;sup>2</sup>For the purposes of this dissertation we will use Model-Driven Engineering as a generic term intended to encompass all model-driven approaches. When discussing a model-driven approach individually, its particular term will be used.

complexity by focusing on one aspect of a system, ignoring other irrelevant details which may hinder the understanding or manipulation of the aspect of interest.

BE can be integrated into an MDE framework by considering the system behavior captured by BE's graphical representation as a modeling dimension. MDE captures the information of a modeling dimension by creating domain specific languages (DSLs) that utilise the notation and abstractions common to the domain. By using the terminology of the domain, the usage of DSLs often encourages domain experts to play a greater role in software development. This benefit, however, must be weighed against the cost of designing, implementing, and maintaining a DSL and the tools to support its use.

Integrating the BE approach into an MDE framework provides benefits for both BE and MDE. BE gains the productivity benefits provided by MDE's leveraging of the increased abstraction provided by models to improve the development and maintenance of software systems. MDE benefits by gaining a language for defining system behavior with an end-to-end scaleable methodology that proceeds all the way from requirements to a deployed system without any miraculous intuitive leaps. This is useful because the use of abstraction in MDE only decreases the likelihood that scaleability will be an issue. Creating larger models in a DSL can still cause increased complexity which can only be prevented if a scaleable methodology is used to build the model.

The choices for development of the BE DSL for system behavior (and any MDE DSL) can be broadly categorised into two approaches [MHS05]: language exploitation and language invention. Language invention involves developing a new language from scratch. Language exploitation creates a DSL by extending an existing general purpose language (GPL), a language that uses generalised constructs to cut across multiple modeling dimensions.

Language invention is used to develop a DSL when existing languages cannot be used to capture domain-specific concepts. Language invention creates DSLs that provide the most benefit to DSL users but they also require the development and maintenance of completely new tools such as an editor, compiler, debugger and simulator. Language invention is most suited to DSLs with a focus on syntax over semantics, with semantics often implicitly defined by model compilers or generators [HM07]. A DSL for capturing system behavior is not particularly suited to language invention, as there is a greater emphasis on the semantics of

10 Introduction

domain concepts in addition to their syntax and structure.

Language exploitation is the most cost effective approach to developing a DSL for a number of reasons. DSLs created by language exploitation can leverage any existing technology developed for the chosen GPL to simplify the implementation and mapping between multiple DSLs. It also allows the utilization of existing editors and the potential to benefit from a user's familiarity with the existing GPL. The utimate success of language exploitation, however, depends on the effectiveness of the chosen GPL at capturing the concepts of the DSL.

Our approach creates the BE DSL for system behavior using language invention because the concepts of BE are unsuited to be captured by existing GPLs. Whilst using language invention to create the BE DSL, however, we also develop BE into a GPL for creating other system behavior DSLs using language exploitation. This enables a family of languages, all based upon the same BE GPL, which allows existing tool support and user familiarity with the BE GPL to be exploited.

This concept of a family of languages is also one of the goals of the unified modeling language (UML), an object-modeling notation that is widely regarded as [Rat05], "... an industry-standard language that allows us to clearly communicate requirements, architectures and designs". In contradiction to its wide adoption as an object-modeling notation, however, UML is widely criticised as an unsuitable GPL for MDE [LCM06, FS06, Th003]. The wider adoption of UML as a host GPL for creating DSLs by language exploitation is hindered by problems with its representation, its methodology and its extension mechanism. These problems, which we discuss in detail in the next chapter, justify the need for a BE GPL for MDE.

Developing BE into a GPL for use in an MDE framework primarily requires an extension mechanism for defining DSLs using language exploitation. To gain the most benefit from MDE, however, a BE model resulting from the new design stage should also be executable. This requires the BE component model to be specified, as previous BE research has not required components with executable behavior, but have instead represented components as variables with an enumerated state [GLYW05]. A toolset consisting of an editor, model transformations, code generation and a virtual machine is also required to execute the BE

1.2 Thesis Hypotheses

models.

After laying these foundations, the remainder of the dissertation is used to demonstrate the wide applicability of this approach in order to establish the suitability of BE as a GPL. We ensure the coverage of several modeling dimensions by utilizing Bézivin's categorisation of three types of MDE applications, namely forward modeling, interactive modeling, and reverse modeling<sup>3</sup> [BBJ07]. Forward modeling involves the most common form of modeling in MDE, which is to create a system from a model. Interactive modeling consists of a system and a model co-existing with each other, with any changes in one influencing the other. Reverse modeling involves the creation of a model from an existing system.

Three case studies <sup>4</sup> were selected within this framework to show a wide cross section of concerns in the addressed modeling dimensions. The three case studies cover the subject area modeling dimensions of consumer electronics, transportation and avionics. They also cover the system aspect modeling dimensions of embedded systems, software/hardware integration and development of field programmable gate arrays from legacy hardware.

## 1.2 Thesis Hypotheses

This dissertation defends the following theses:

- 1. Mainstream Sw&SE approaches, generally, do not adequately address scaleability.

- (a) These approaches commonly use abstraction to decrease the likelihood that scaleability will be an issue.

- (b) These approaches do not build a system from out of its requirements and it is common for a miraculous intuitive leap to occur between the requirements and the specification, design or deployed system.

<sup>&</sup>lt;sup>3</sup>Bézivin used the term forward engineering and reverse engineering instead of forward modeling and reverse modeling. He also used the term models-at-runtime as opposed to interactive modeling, though the central concepts of these terms remain unchanged.

<sup>&</sup>lt;sup>4</sup>The term 'case study' as used throughout this thesis, is not intended in the sense of the research methodology of the same name (the case study research methodology [Yin09]). Instead, each case study in this dissertation should be considered as a worked example that demonstrates the principles upon which it is based.

12 Introduction

- 2. Scaleability can be addressed better by:

- (a) Using an approach with a minimised local problem space that remains constant regardless of the size of the global problem space.

- (b) Using an end-to-end approach that begins at the initial requirements and proceeds all the way to a deployed system without any miraculous intuitive leaps. An end-to-end approach provides the maximum productivity benefit and discourages the need for intuition to be used in the approach.

- 3. Extending BE to have a design stage which is developed within an MDE framework will leverage the scaleability of BE and the productivity benefits of MDE to:

- (a) Create an end-to-end methodology.

- i. The system behavior modeling dimension of BE is suited to describing a system at the stages of requirements, specification, design and deployment.

- (b) Create a widely applicable approach.

- i. The system behavior modeling dimension of BE is already widely applicable to a multitude of problem domains.

- ii. The applicability of the BE approach can be improved further by using an extension mechanism to create domain-specific languages defined by BE.

- iii. The MDE concept of platform-independence and transformations can improve the applicability of the approach to a larger area of solution domains.

- (c) Create a scaleable methodology.

- i. BE is already proven to be scaleable for requirements analysis of large-scale systems in industry.

- ii. A scaleable methodology for design with BE can be developed by extrapolating the principles that make BE scaleable for proceeding from requirements to a specification and adhering to them whilst proceeding from a specification to a design.

1.3 Contribution 13

#### 1.3 Contribution

The contribution made by this dissertation is summarised below:

- 1. The existing BE approach has been extended to support design and deployment.

- (a) The stages of specification and design have been clearly separated and the design decisions required to proceed from a specification to a design are outlined.

- (b) A component model for BE has been defined that describes how executable components can be integrated by a deployed BE model.

- (c) An extension mechanism is described that enables DSLs to be created that use BE as a host GPL.

- (d) A toolset that consists of an editor, model transformations, code generation and a virtual machine has been developed to support the deployment of BE models.

- 2. The resulting approach provides a new GPL for MDE with the following characteristics:

- (a) It uses a visual language with a small core notation with formal, well-defined semantics.

- (b) It is linked to a scaleable methodology that is applicable all the way from requirements, through specification and design to a deployed system.

- (c) It can be applied to Bezivin's [BBJ07] three types of modeling within MDE:

- i. Forward modeling is demonstrated by deploying a BE model on an embedded controller.

- ii. Integrated modeling is demonstrated by investigating early-stage hardware/software design by combining this approach with Modelica, a mathematical modeling language.

- iii. Reverse modeling is demonstrated by building a BE model from an existing legacy system that is then deployed on a new platform of a Field Programmable Gate Array.

14 Introduction

3. A new approach to integrated hardware/software development is introduced called comodeling. Co-modeling is intended to supplement the existing practice of co-design which is applied later in the later stages of development. Co-modeling has the following characteristics:

- (a) It provides a framework to investigate the suitability of design decisions applied to a specification consisting of a mixture of hardware and software components.

- (b) It helps locate and resolve defects across the software/hardware boundary early in development when they are cheaper and easier to resolve.

- (c) Simulation of co-modeling scenarios provides a graphical and documentable result that can be used to determine the specifications of sensors and actuators operating in a range of environmental conditions.

## 1.4 Thesis Structure

This dissertation is organised into five parts with a total of eight chapters. Part I - Introduction and Background is comprised of four chapters, beginning with this chapter, Chapter 1: Introduction.

Chapter 2: An Overview of Model-Driven Engineering provides a more indepth discussion of the state of the art in MDE that forms the foundation for the objectives and approach of this dissertation. This discussion begins by defining the goals of MDE, and exploring their origins. Existing approaches to MDE are then investigated with a focus on their ability to capture system behavior. The appropriate representation, methodology and extension mechanism of a new MDE GPL for system behavior is then discussed.

Chapter 3: Introduction to Behavior Engineering provides an introduction to BE for readers not already familiar with the approach. Readers who are familiar with BE may prefer to omit this chapter. The chapter details the representation and process of BE by means of a case study involving modeling the requirements of a simple microwave oven. The case study is used to demonstrate how BE is used to formalise natural language requirements by translation; perform a fitness for purpose test by integrating the formalised requirements;

and develop a specification by locating and correcting defects in the integrated requirements. Related research in the area of Behavior Engineering is also discussed.

Chapter 4: Design with Behavior Engineering describes an extension to BE which provides better support for design. This chapter begins by addressing why BE requires a design stage as opposed to using a BE specification with other conventional design approaches. Following this the BE component model and extension mechanism are described. The chapter concludes by describing the process of the design stage which is illustrated by continuing the design of the microwave oven from the specification produced in Chapter 3.

Part II - Forward Modeling discusses the creation of a system from a model, which is perhaps the most common use of MDE. Chapter 5: Behavior Engineering of Embedded Systems concludes the microwave oven case study by illustrating its deployment on an embedded controller. This illustrates that BE can be utilized for the system aspect of embedded systems. This chapter also introduces the toolset which has been created to support design with BE. The toolset consists of an editor for describing BE models; model transformations to make BE models executable; and a virtual run-time environment for executing BE models tailored specifically for embedded systems.

Part III - Integrated Modeling deals with the difficult case of a model and a system co-existing and influencing each other. This form of modeling often gives rise to wicked problems: problems with complex interdependencies such that the solution of one aspect of the problem often creates or reveals previously unidentified problems in other aspects. Chapter 6: Co-Modeling with Behavior Engineering and Modelica introduces an example of integrated modeling that occurs when developing a system composed of integrated software and hardware components. This is often addressed by co-design, which deals with partitioning functionality onto a mixed architecture of software executing on a central-processing unit and specialised hardware implemented on a field programmable gate array. This dissertation introduces co-modeling, which is a new approach that also deals with integrated software/hardware design but at an earlier stage of development than co-design. Our approach to co-modeling is introduced which integrates BE with Modelica, a mathematical modeling language. Co-modeling is demonstrated with a case study involving the development of an automated train protection system which monitors a train driver and

16 Introduction

takes control of the train if a dangerous situation is not met with an appropriate response. The developed co-model is used to investigate co-modeling scenarios and to determine the effect various combinations of sensors, actuators and hardware platforms have on the system's behavior. The case study also demonstrates the Behavior Run-time Environment, which differs from the embedded version by utilizing attributes, an expression parser and parameterized messages. The chapter concludes with a discussion of how co-modeling can be a useful tool in building large-scale systems.

Part IV - Reverse Modeling deals with creating a model from an existing system. A common application of this form of modeling is to model legacy systems which can then be migrated to a new platform. Chapter 7: Behavior Engineering of Hardware Systems introduces a migration approach to legacy systems in which a BE model is used as an intermediary. This chapter uses a real case study from industry. The case study deals with a small portion of outdated circuitry built with transistor-transistor logic (TTL) integrated circuits (ICs) that need to be replicated in a field programmable gate array (FPGA). The circuit schematic is captured in a BE model by using a domain-specific extension. The BE model is then used to generate VHSIC hardware description language (VHDL), a hardware description language that is used to define a FPGA. To demonstrate the advantage of using BE as an intermediary (as opposed to a direct mapping from a domain-specific language) the BE model is used to perform failure mode and effects analysis, a procedure commonly applied to BE models developed from software requirements.

Part V - Discussion comprises *Chapter 8: Discussion* which concludes this dissertation. This chapter gives an overview of the material presented to elicit the contribution provided by this dissertation. Ideas for future work are also discussed.

2

# An Overview of Model Driven Engineering

In this chapter we review existing model driven engineering (MDE) approaches for developing software-intensive systems. We analyse the suitability of the languages used by these approaches, particularly for capturing semantically-rich system behavior.

This chapter is organised into three sections: The first section of this chapter investigates the origins and goals of MDE in more detail. The core concepts of MDE and the reasons for their emergence are described, and whether MDE has the potential to live up to its claims. The second section is a review of the state of the art approaches to MDE. The review focuses on the model driven architecture (MDA), a prevalent view of MDE. Three different realisations of MDA are discussed in conjunction with other related approaches. The third section argues that there is a need for a new general-purpose language for capturing the modeling dimension of system behavior. The section elicits the special characteristics of

this modeling dimension that warrant the development of a new general-purpose language in an MDE framework. It addresses the deficiencies of the current MDE approaches at capturing this modeling dimension by investigating what representations and methodologies are required for a new MDE GPL for capturing system behavior.

## 2.1 Origins and Goals of MDE

In the Introduction, we defined MDE as a model-centric approach to software development. Rothenberg vividly describes the utility of modeling [Rot89],